Dear team,

My customer our LM74700-Q1 waveform, and they have some questions as attached. Could you please help answer it? Thanks.

Thanks & Best Regards,

Sherry

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Dear team,

My customer our LM74700-Q1 waveform, and they have some questions as attached. Could you please help answer it? Thanks.

Thanks & Best Regards,

Sherry

Hi Sherry,

Thanks for reaching out. Let me check and get back to you by Wednesday.

Thanks and best regards

Divyanshu

Hi Divyanshu,

Could you please help answer my question?

Best Regards,

Sherry

Hi Sherry,

For questions 1 and 2:

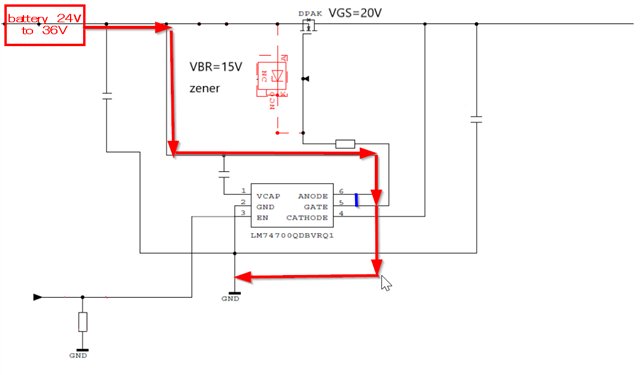

When EN of LM74700 is pulled low, the gate and source voltage should be the same. Do GATE-ANODE should ideally be zero. Did the customer face the same issue with multiple different ICs?

For question 3:

Yes, a zener diode can be used to protect the FET from exceeding it's Vgs rating. But since the maximum Vgs can go is 14V for LM74700 and the FET itself is 20V rated, the zener diode protection is not really required.

Thanks and best regards

Divyanshu

Hi Divyanshu,

Thanks for your reply!

1. Due to sample limit, they only have one board, so they only test one chip. Have we test such waveforms? Could you please help test it one our EVM based on customer's test condition?

2. When EN pin is disabled, is there any leakage current passing through below path? Because ANODE is connected to Gate pin internal when EN is disabled. In my understanding, Gate pin should be connected to GND in internal circuit, right?

For the third question, we want to make further

Hi Sherry,

1. Let me test this on EVM and get back to you by early next week.

2. When EN pin is disabled, very low shutdown current will flow from the supply to the ground. This leakage current is limited to around 1uA.

Thanks and best regards

Divyanshu

Hi Divyanshu,

Thanks for your help!

When you test it, please set the same test condition with the customer. Thank you!

Thanks & Best Regards,

Sherry

Hi Sheer,

I have tested with same customer conditions in the lab with our EVM. As can be seen in attached results, gate exactly matches anode voltage when given a 5.7V supply with EN pulled low. Please try testing again with the same EVM. If you still face an issue, please try with a different EVM/sample as there is a possibility of damage during testing.

Input voltage (anode):