Other Parts Discussed in Thread: LM34966-Q1, UCC28C41-Q1, LM5156

Dear team,

My customer plans to use our device as flyback controller(Primary-Side Regulated).

1. Our device doesn't have SCP/short circuit protection, do we have any solution to achieve this function? For example, the output load is shorted.

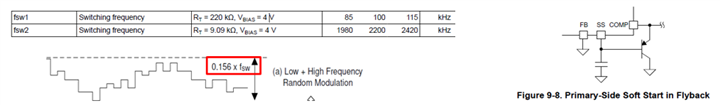

2. Compared with LM5156-Q1, LM34966-Q1 doesn't include the spread spectrum function. My customer is sensitive to the cost, so they also evaluate our LM34966-Q1. They want to know whether we can add external circuit at RT pin to achieve the spread spectrum function for our LM34966-Q1.

3. Our LM5156-Q1 use internal transconductance error amplifier, and some devices use normal amplifier, for example, UCC28C41-Q1. Could you please tell me why we use transconductance error amplifier instead of the normal one?

Thanks & Best Regards,

Sherry