Hi,

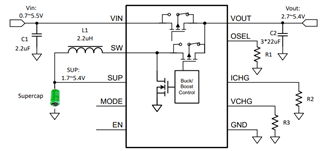

I am designing a back-up power circuit including a primary battery and a supercapacitor.

Main use case for the supercap is to supply power while replacing the battery.

Current design is a cascade: first stage running on battery and second on supercap.

Now the leakage current of the supercap consumes a lot of juice from the battery.

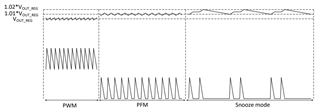

Is there a better way to design, e.g can two TPS61094 chips be connected in parallel?

Configuring different output voltage decides priority?