Other Parts Discussed in Thread: LM5176

I started with the LM5176 design spreadsheet and the WEBench design: https://webench.ti.com/power-designer/switching-regulator/customize/18?noparams=0

I tried to include the schematic below but the quality of included images is very poor so if the link doesn't work then to recreate it in WEBench enter the design parameters minimum input voltage 12V, maximum 24V, Vout 18V and Iout up to 10A.

On reviewing the LM5176 design and WEbench design against the datasheet, Cslope was changed to 390pF, CC1 to 47nF and CC2 to 1500pF..

Because of part availability L1 is IHLP6767GZER4R7M01, M1 and M2 are SIDR626LEP-T1-RE3 and M3 and M4 are STL260N4F7

I have had four dev boards made and tested them all up to around 130W and have three main issues:

Firstly one of the boards does not start up at 12V unless it has a 2W load.

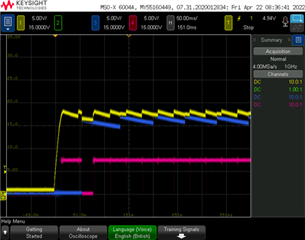

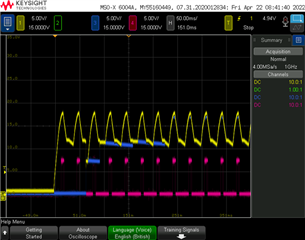

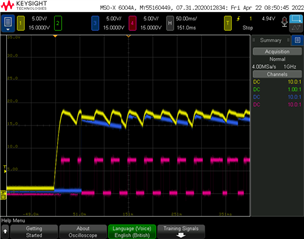

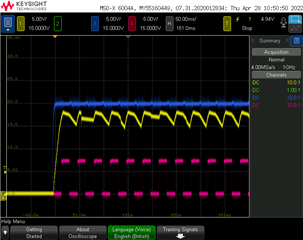

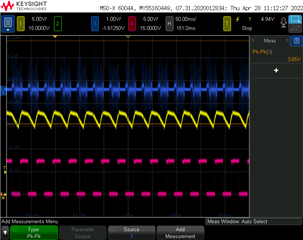

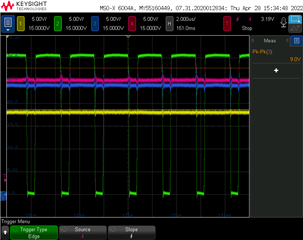

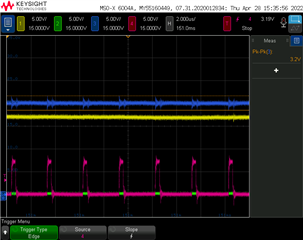

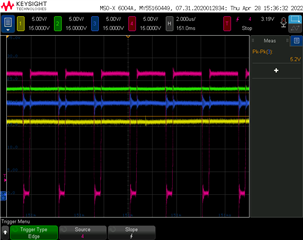

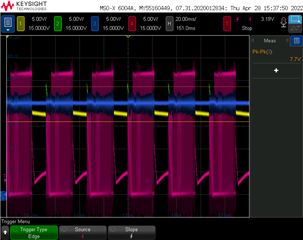

Secondly, all of the boards have instability between 17V input and 20.5V input unless they have a significant load, for example at 20V the stability only recovers with a 1A load (17.5W).

Thirdly, the overall efficiency is only around 93% at 100W with 24V in and 91% at 100W with 12V in compared to the design target of 98.3%.

So my questions are:

Can I make any changes to improve stability?

Can I make any changes to improve the overall efficiency?