Hi,

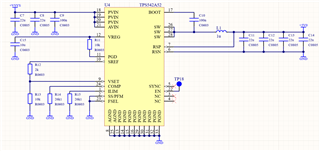

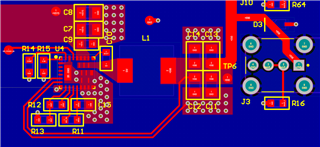

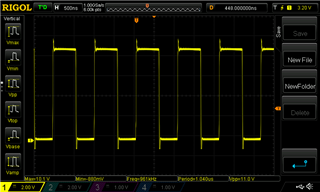

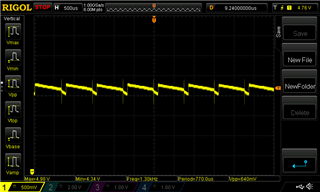

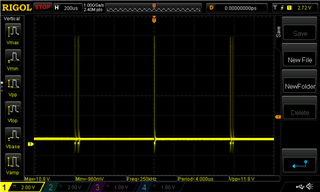

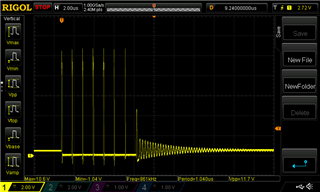

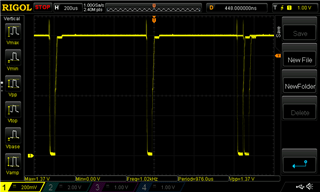

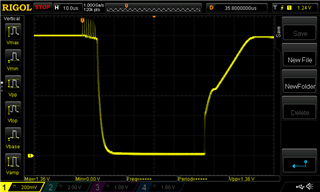

I designed PCB with TPS542A52 and it does not work properly. When power turns on, output goes to 5V but when we connect some load to it (like 100 mA) it immidiatelly goes down and after load is removed it does not recover to 5V again, only to ~0.4V. I have 3 PCBs and every behave the same way.

The strange thing is that i did exactly same schematic and layout before in other PCBs and it worked perfectly fine. It sounds like bad soldering but I also checked it.

I tried to pull-up enable pin to some voltage (3.3V) to be sure that enable pin is above 1.2V threshold. Then output do not charge to 5V even without attached load - it stays at 0.4V.

So my question is: Do you know what could be a cause of this behaviour?

Best regards

Tomasz

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.