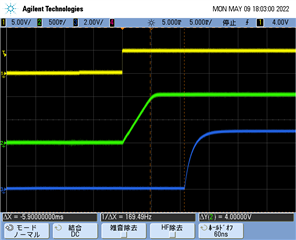

When LMZ31506 startup, power good output is delayed about 6ms.

Please refer below waveform;

※ch1: Vin (5V), ch2: Vout (1.03V), ch3: PWRGD

Is there any reason for PWRGD delay?

If there detailed schematic, please let me e-mail address.

By the way, pullup resister is 10kΩ, but also output side (the other IC's enable) connect 1MΩ pullup.

Is 1MΩ possibility to involve the PWRGD delay?

Best regards,

Satoshi