Hi Team,

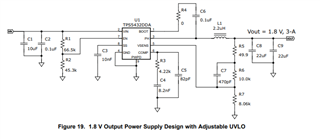

We are designing a buck converter using the IC TPS5432DDA.

The required output voltage is 1V.

The input voltage is from a Li-ion battery with a nominal voltage of 3.7V (2.8V to 4.2V).

Attached is the designed circuit.

The feedback resistors are a 10K resistor with a 470pF feed-forward capacitor and a 42.2K resistor to the ground.

I want to adjust the output voltage of the buck converter. So I am using the DAC of the processor to feed the VSENSE pin of the TPS5432DDA.

1). Is my calculations correct?.

2). Th output equation of the TPS5432DDA is given as

In equation 16 for the output voltage, the resistor R5 (49.9E) is not included. Why is that?.

I hope that resistor too has an effect on the output voltage.

Please correct me if I am wrong.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.