Other Parts Discussed in Thread: TPS2663

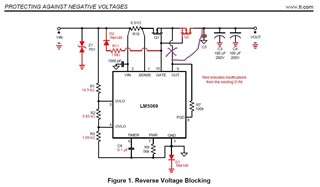

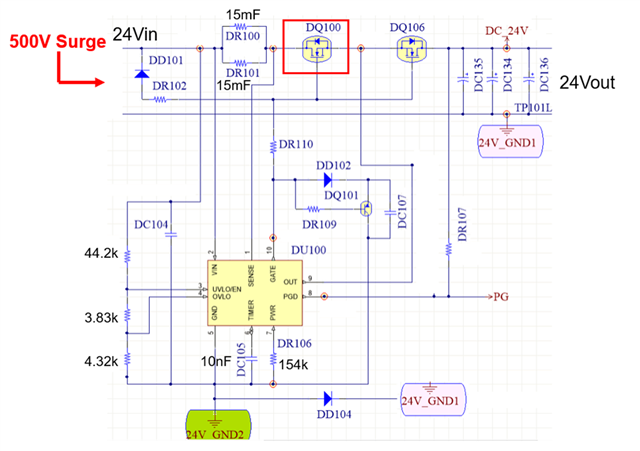

Customer would like to ask if the OUT pin of the LM5069 is connecting to VOUT rail ok? is there any side effect here? Or what else test you suggest to do with this configuration? Please see below plot for details.

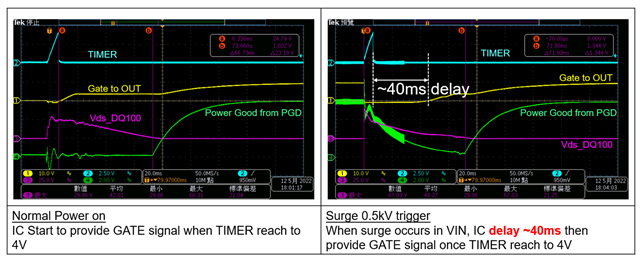

Since if customer following the topology on application report of the SNVA683, the recovery time (During OV protection Q1 and Q2 are turned OFF) is longer with several hundred ms and causing the system power/Flyback reset during surge event. Power reset is NOT allowed in servo drive application.

After change the connection to VOUT, recovery time will become shorter about several ten mS, thus system/Flyback could not go into the shutdown with this configuration.

Surge: 8/20uS with 500V on the 24Vin rail.

VIN: 24V

application: Servo Drive in Modeling machine