Dear,

I met a problem in the simulation by LTspice.

Short description of the circuit:

There's a current limitation (10mA) after the Voltage Source, the input side of TPS7A24 has 470uF capacitor, the output side has 20uF capacitor.

Problem in the simulation result:

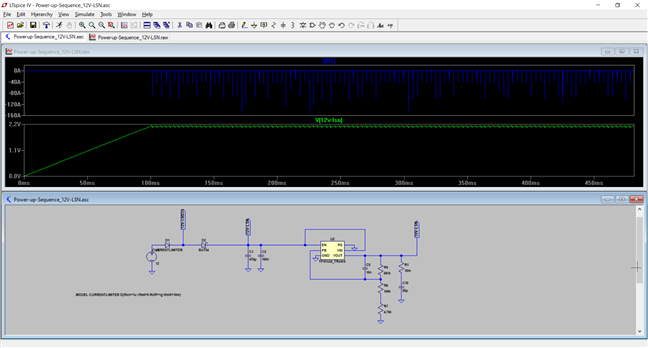

The input voltage was stuck at ~2.1V and cannot rise, so there's no voltage output, it seems there's some kind of current limitation (ilim) in the LDO model, but how can I do with Cout=20uF?

Thanks.

Pls see the screen shot of the simulation below (the blue line is the current through Cout) and the .lib file and the source file which I used.