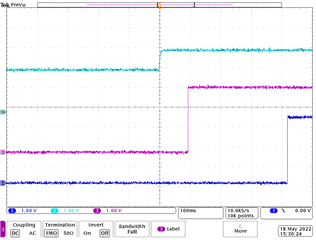

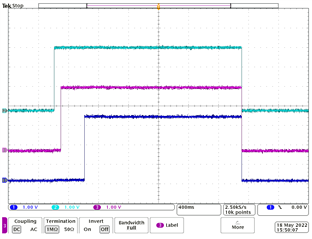

We're using a TPS38600 which monitors 4 different rails, each using a 22 nF capacitor on the Cct pin. Per the equation pulled from the datasheet, Cct(nF) = [Tdelay(ms) - 0.5(ms)] X 0.242, we would expect a delay time of around 95 ms.. However, we're measuring a delay time between the last rail crossing its threshold and the reset being deasserted (pulled up) to be around 140 ms. We are using a 100 kohm pull-up resistor (and even tried a 20 kohm pull-up resistor) on the RESET line. The 22 nF capacitor is also ceramic per recommendation of the datasheet to mitigate any leakage. I would expect any stray capacitance on the board to be in the pF range and not be a huge contributor to the almost 50% increase in delay time we're seeing. Is there that much potential error in the calculation vs performance of the reset delay time or maybe I'm missing something else? Thank you

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.