Dear team,

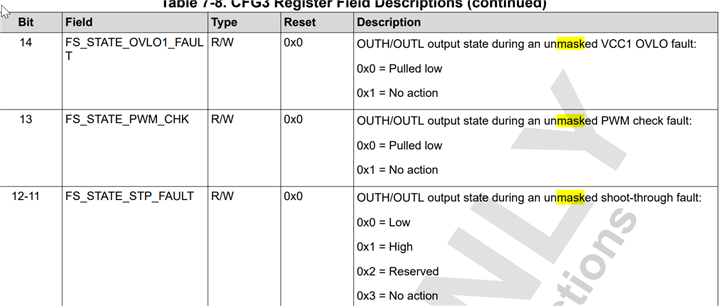

1. If one fault is masked, then nFLT pin won't pull low. Does the FS_STATE_XXX operate? For example, if VCC1 OVLO fault is masked, and we set bit14=0. When this fault occurs, OUTH/OUTL will have no action due to being masked, right? It means that our device will ignore this fault totally.

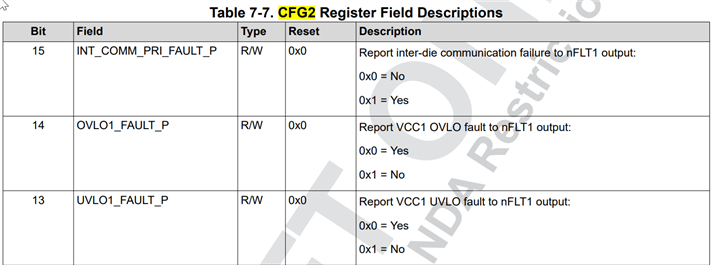

2. In below picture, bit 15=0 means fault won't be reported while other bits have the contrary logic, bit 14/13=0 means reporting the fault. Is it a typo? Or we have a special reason for that?

Thanks & Best Regards,

Sherry