Hi,

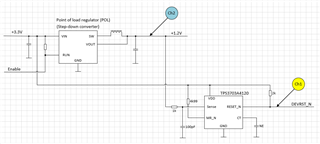

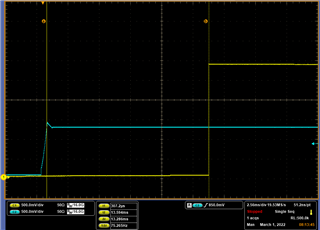

we are using TPS3703A4120 device, which provides a fixed reset delay time of 10 (+/-3) ms. At startup the startup delay has to be added which typ. 300us.

Q1: What extreme values can we expect for startup delay? Especially the max. value is of interest.

Q2: According note 4: "During the power-on sequence, VDD must be at or above VDD (MIN) for at least tSD + tD before the output is in the correct state". So, reset output assertion starts if VDD has to reach at least 1.7V and SENSE input has within range voltage. Is this correct? What means "...for at least tSD+tD"? Could this be even longer time and if yes what is the max. time tSD+tD?

Q3: Section 9.1.2 CT Reset delay time: "To determine which option is connected to the CT pin, an internal state machine controls the internal pulldown device and measures the pin voltage. This sequence of events takes 450 μs to determine which timing option is used." This parameter is not listed at all in datasheet timing requirements (section 7.6). How does this value apply. Is this an additional delay?

Please note: all those questions pop up after comparing measurement results (tD_measured = 13.21 ms) with the maximum expected value according datasheet (13 + 0.3 ms). Even with consideration of the startup delay we are at 25°C close to the maximum value according worst case analysis, which is weird.

Thanks in advance!

Best Regards,

Andreas N.