Other Parts Discussed in Thread: TPS62824, TPS82084

Hello,

I would like to use the Power Good (PG) output pin on the TPS62080 to enable a second TPS62080 (or similar) supply. I'm planning to add the recommended pull up resistor from the PG pin to the output voltage (Vo).

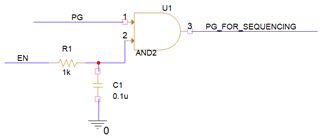

My concern is that based on the power good logic table in the TPS62080 datasheet (Table 1) the power good signal will be High Z when the device is not enabled. I have a delay between when the TPS62080 input voltage ramps up and when I enable the device. During this time the power good signal will be floating per table 1. If I have this power good signal connected to the enable on a second TPS62080 then this enable will now be floating as well. In the pin description of the TPS62080 its says to not leave the enable pin floating. I do not want the enable to be floating and potentially turn on the second device early.

How do you recommend power sequencing with these converters to avoid this issue? Or is there a reason this is not a concern?

Thanks.