请教一下,TPS548D22 SW开关抖动比较大是什么原因?是因为FSEL被干扰或者AGND被干扰吗?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Please forgive me if I misunderstand your question, but I had to use Google Translate.

请教一下,TPS548D22 SW开关抖动比较大是什么原因?是因为FSEL被干扰或者AGND被干扰吗?

"What is the reason for the large jitter of the TPS548D22 SW switch? Is it because FSEL is disturbed or AGND is disturbed?"

No, it is not a result of a disturbance in FSEL or AGND. The TPS548D22 uses TI's D-CAP3 control topology, which is a variation of Constant On-time Pulse Width Modulation that uses an internally generate ramp to emulate an ESR ripple voltage on the output. This is a form of Pulse Frequency Modulation (PFM) that sees natural variation in the cycle by cycle pulse width with constant pulse widths, which is why you see virtually no jitter on the pulse width of the center pulse.

The level of jitter commonly seen with this form of control depends on the down-slope of the internal ramp, which is selected using the FSEL pin. A larger ramp, (Lower R) will produce less cycle by cycle period jitter but respond more slowly to transients. A smaller ramp (Higher R) will produce more cycle by cycle period jitter but respond more quickly to transients.

The amount of external capacitance, capacitive ripple, and ESR ripple can also affect the level of jitter observed. Systems with less output capacitance, more capacitive ripple, which is out of phase with switching, and lower ESR, will generally display more period jitter.

Additionally, lower output voltages, which have longer off-times and shallower falling ramp slopes, generally produce more jitter as the inherent noise in the off-time comparator produces more uncertainty in the timing of the off-time detection. However, the effect of the frequency jitter on the output voltage is generally small, and represents less than 1mV at the RSP node.

While the jitter is expected, noise injection into the differential sense RSP - RSN will also add to jitter as the control loop attempts to cancel this noise injection into the sensed output.

Thank you for your reply. So how much the jitter should be controlled in Constant On-time control topology, or there is no requirement for it?

It depends on the needs and details of the design, but generally +/- 10% (20% total) of the switching period is normal. Random pulse frequency jitter like this will provide natural spread-sprectum, reducing the peaks and spurs in the EMI profile of the design.

How much output ripple does the design have?

What is the FSEL selecting for the internal ramp generator?

The 3.3V output capcitor is 600uF pure MLCC, and the FSEL for the internal ramp generator is Rx3 according to the datasheet. The output ripple is about 10mV, but the jitter is over 20%. After adding the output MLCC to 800uF, the ripple is reduced to 6mV, and the jitter is reduced to 16%. Could I increase the ramp compensation in addition?

Instead of increasing Cout, If you want to decrease your jitter, I would recommend you update the FSEL resistor selection to select the Rx2 or even Rx1 ramp instead, that should reduce the jitter that you are seeing by increasing the ramp slope.

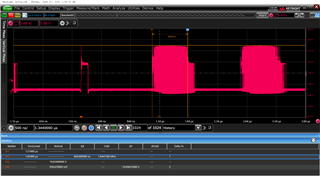

However, the jitter in the waveform you shared is less than 20%. The nominal switching period is 1.6μs and the jitter range is 274ns. 20% of 1.6μs would be 320ns.

This waveform shows the jitter of 0.92V power rail at 19A. After selecting the R/2 ramp and increasing Cout, the jitter at 19A is still over 20%, while the jitter at 0A is 15.3%. What can I do otherwise to decrease the jitter?

Hello Jiajun,

Peter is out of office this week. Someone from the team will help look into this.

Thanks!

Tahar

Hi Jiajun,

Another thing to look at is the noise injection into the differential sense RSP - RSN. Please add a 1nF ceramic cap parallel between the RSP and RSN pins to see if that helps reduce the jitter.