Other Parts Discussed in Thread: LM3881, LM3880

I want to input the output (+5.0V DC) of the TPS23257A to the VCC pin of the LM3881 to satisfy the power supply rising sequence and power supply falling sequence.

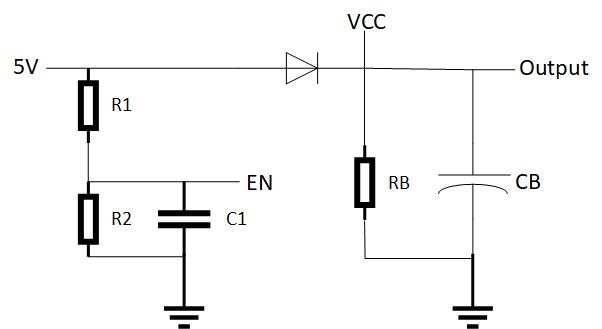

We have already confirmed that +5.0VDC can be output from the TPS23257A using the actual device from the circuit below.

We believe that +5.0V must be input to the VCC pin before the EN pin exceeds the Threshold Level (+1.22V) to satisfy the power rise sequence of the LM3881.

The datasheet states that the rise of the EN pin can be delayed by connecting an external capacitor to the EN pin.

Is it possible to meet the power rise sequence here?

We believe that in order to satisfy the power supply fall sequence of the LM3881, the voltage must be held long enough to allow enough time for the EN pin of the LM3881 to go LOW.

We believe we should add an external capacitor to hold the voltage, where should we add it?

Also, is there any other way to satisfy the power supply falling sequence?