Other Parts Discussed in Thread: BQ77904

Hi there,

I have a question concerning the Application Report "BQ77904, BQ77905 Functional Safety FIT Rate, FMD, and Pin FMA":

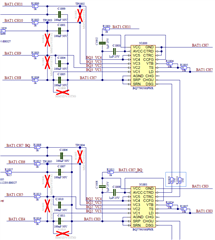

On page 7 the open mode failures are described. Concerning the VDD Pin I assumed, that in case of an interruption of the series resistor supplying VDD during the run state, the IC would switch off the CHG/DSG FETs and enter safe state. In our stacked 4S configuration of the BQ77905 the VC5 potential is connected to VC4. The schematics is shown below:

In case of an interruption of VDD, VC4 and VC5 still have the supply potential connected. When measuring the voltage at the interrupted VDD I was surprised to measure a voltage of 12.15V when applying a cell-voltage of 4V per cell (VDD equals to CV3 + 0.15V). Therefore with an open supply line the IC was still working except for the overvoltagethreshold of VC4. This failure state was not detected and could result in a dangerous behaviour. When I disconnected VC5 from VC4 and left the pin (VC5) floating the IC lost it's supply completely and therefore the CHG/DSG FETs turned off.

Can you explain why there was still a supply present as long as VC5 was connected?

From section 8.3.10 and figure 8-10 of the datasheet I assumed that VC5 had to be connected to the highest cell potential in case of a 4S configuration. Can you explain why this is required and whether it would be possible to let this pin float or short it to ground when it is not used?

Do I have to expect other differences on the FMA behaviour of the IC when using it in 4S and not 5S mode? We assumed that all Pin-failures would be the same for 4S and 5S except for small deviations concerning CV4 and VC5.

Kind regards

Bernhard Baier