Other Parts Discussed in Thread: PMP30963, CSD18536KTT, CSD17318Q2, LM5152-Q1, LM5152EVM-BST, CSD17581Q3A, LM5176

Hello Team,

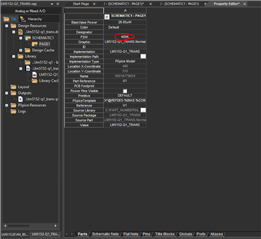

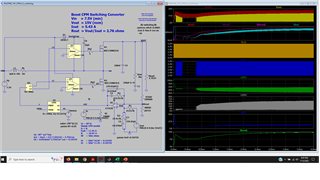

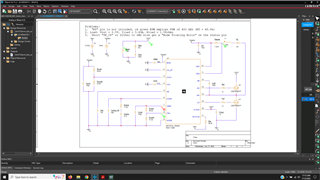

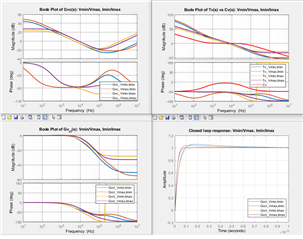

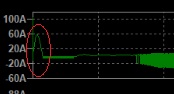

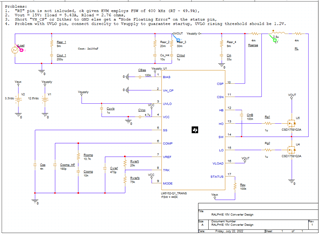

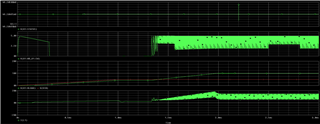

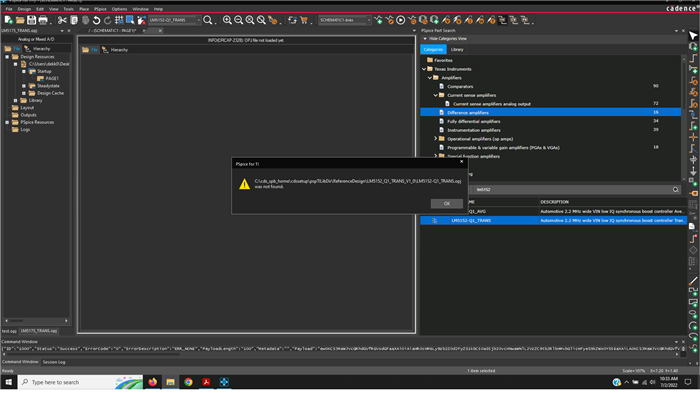

My customer gets the following error (see attached pic) when they try to open the parts reference transient simulation/design.

Any thoughts on how to get past this problem?

Regards,

Renan