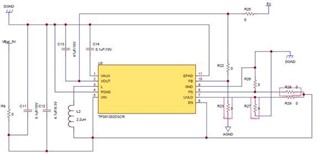

I designed the following circuit for our prototyping product.

In this case, the efficiency is too low.

Vin = 3V, Iin = 20mA, Vout = 5V, Iout = 8mA, Efficiency = 67%

Power save mode = Enable

Do you think anything wrong to our circuit?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I designed the following circuit for our prototyping product.

In this case, the efficiency is too low.

Vin = 3V, Iin = 20mA, Vout = 5V, Iout = 8mA, Efficiency = 67%

Power save mode = Enable

Do you think anything wrong to our circuit?

Hi Togo,

Thanks for reaching out on E2E.

Please double check that PS pin is short to gnd.

Also, can you take the waveforms of Vin, SW, Vout and iL?

How do you test the voltage and current value? Did you read them from supply and e-load or connect with digital multimeter?

Regards,

Bryce

Hi Bryce,

Thank you for replying.

Would you please check the following answer.

PS pin is shorted to gnd.

I read the current value with connected with digital multimeter.

Best regards, Togo

Would you please check the attached file for waveformsWaveform of TPS61202.xlsx

Hi Togo,

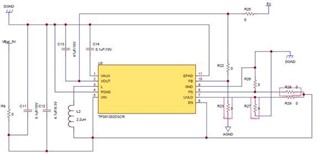

What is your input supply? The input voltage ripple is so large when the device starts switching. Can you also probe the inductor current?

Regards,

Bryce

Hi, Bryce,

Input supply is the regulated DC power supply.

And would you please see the inductor current of attached file.

Waveform of TPS61202_V2.xlsx

Best regards, Togo

Hi Togo,

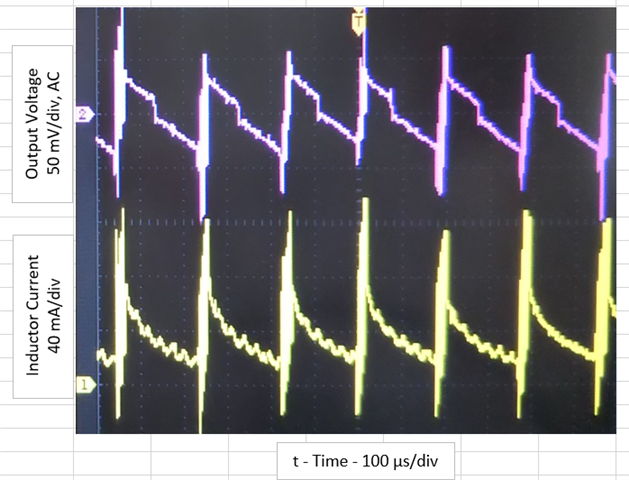

The inductor is weird, it's quite different from the datasheet shows. When SW stops switching, the inductor should decrease to zero, so power consumption is low.

Below are the comparison between your test result and datasheet result:

Can you forward your layout file to me to check if it's ok?

Regards,

Bryce

Hi, Bryce,

Would you please see the layout of attached file.

Waveform of TPS61202_V3.xlsx

Best regards, Togo

Hi Togo,

The Cin cap layout is bad. The input capacitor should be placed as close as possible to the IC.

The Cout cap layout is also bad. The output ceramic capacitor must be placed as close to IC as possible. The reason is the current of loop formed by power mosfet Q, high side FET (or rectifying diode), output capacitor is discontinuous. The loop parasitic inductance in high di/dt current path will generate high voltage spikes at output and across power MOSFETs. Details can be seen in this app note.

Regards,

Bryce

Hi, Bryce

I am Togo's colleague, Keisuke.

Thank you for your reply.

I have two questions.

1.In case we put the Cin / Cout cap near the IC, how far do we need?

2.In the case of the xlsx file, GND of Cout cap is not directly connected to IC GND.

Due to the distance and the connection, Cout cap layout is bad, isn't it?

Best regards,

Suzuki

Hi Keisuke,

Thanks for your update.

1. For Cin and Cout layout, the power loop should be as small as we can.

2. For the layout in xlsx file, the GND trace is a bit thinner which could result in higher parasitic parameters compared with EVM layout.

Also, the GND trace of power loop is under the inductor, which is not recommended because the GND can be disturbed through high switching noise.

Regards,

Bryce

Hi Bryce,

Thanks for your reply.

I got it, and fixed the layout.(ref: new_layout.png)

Maybe, the new layout gets better, isn't it?

Best regards,

Keisuke

Hi Keisuke,

I don't find the Vin-Cin-GND and Vout-Cout-GND loop, it seems the loops end at 9pin, right? If so, the loop is larger.

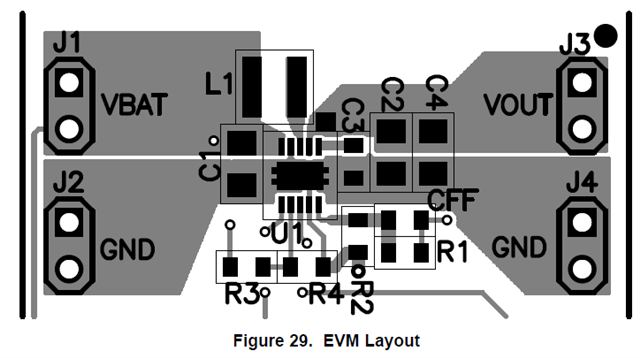

Please refer to the next EVM layout for recommendation.

Regards,

Bryce

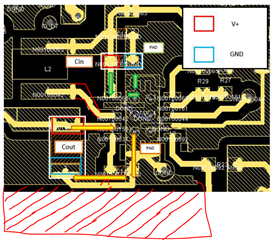

Hi Bryce,

Thanks for your reply. I realize it's error.

I change the GND pattern of pad, and the loops smaller.

The new layout is attached to this message.

*********************

Here,

1) Cin loop is green line:

Cin Voltage side > IC input > IC ground > pad GND > Cin GND side

2) Cout loop is yellow line:

Cout Voltage side > IC input > IC ground > pad GND > Cout GND side

*}*****************

Regards,

Keisuke

Hi Keisuke,

The layout is better. But the trace of Vout-Cout is still thin, recommend to pour the ground plane to reduce parasitic inductance.

Regards,

Bryce

Hi Keisuke,

Thanks for your update. Please let me know if you have any more questions.

Regards,

Bryce