Hi team,

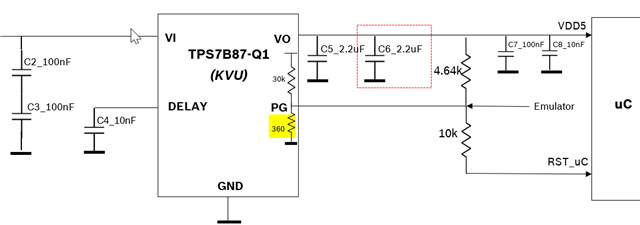

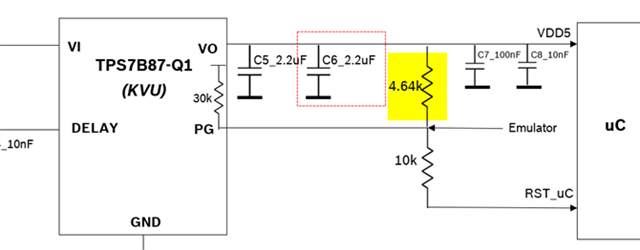

One of my customer would also like to know if a pull-up resistor can be connected externally between the PG pin and Vo, since there is a requirement from the microcontroller side. What would be the impact on PG behavior due to this addition?

Regards,

Naveen