hi team:

My customer report the TPS53355 have two devices can not output 30A as usual, only 21A. But if the input voltage is increased, the output current capability will also increase.

the situation of abnormal board is as below:

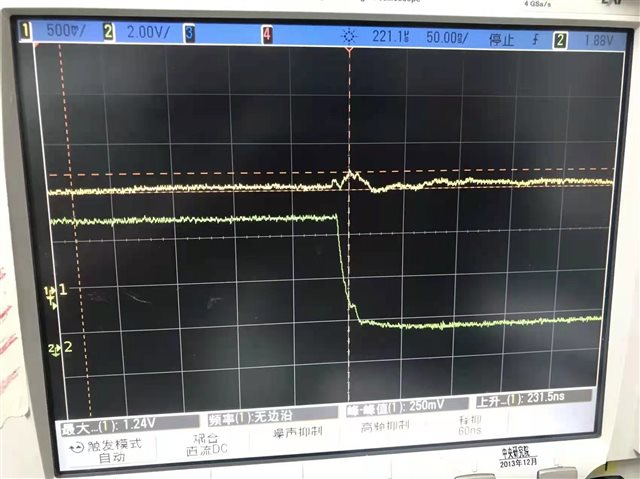

1. 5.5V input, 1V output, it is estimated to be about 21A.

2. 7.5V input, 1V output, it is estimated to be about 27A.

But normal boards, 5.5V input, 1V output, have about 27A..

experiments we have try:

1.The normal input is about 5.4V. If the input is raised to about 6V, other conditions remain unchanged, and the output load current can be increased by about 4A.

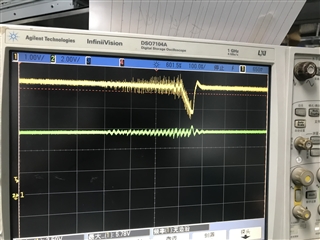

2. The first abnormal board adds an input capacitor of 200uF, the second abnormal board adds 300uF, and other conditions remain unchanged, the output load current can be increased by about 3A.

Basic inspection:

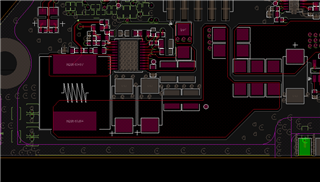

1. No virtual welding, NO false welding.

2. Using the fan to cold down. without over heat.

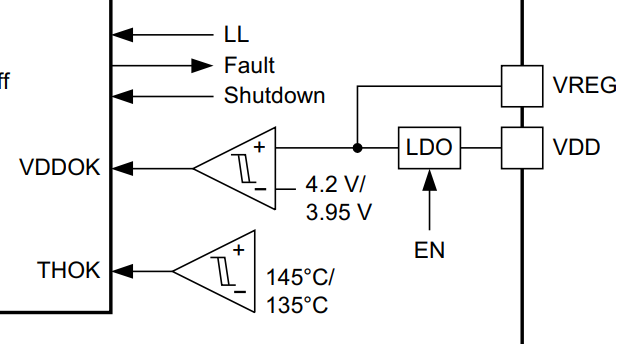

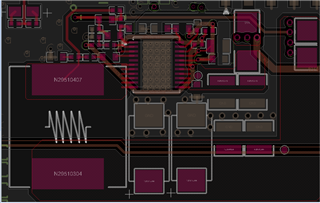

SCH upload as attached.

Can you help to review this SCH? And confirm why the above 2 experiment can increase the loading capability ?

TKS in advance.