About TPS7A2018PDQNR (Vout 1.8V/ package X2SON),

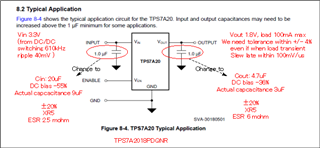

1. We are thinking that select the Vin/Vout capacitance as below figure condition.

Do you think that Is diagram condition no problem for meet our need spec?

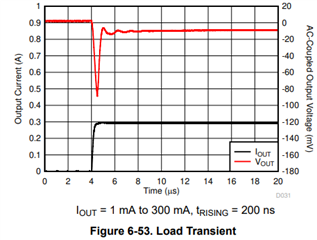

Our need spec: Vout 1.8V tolerance within ±4%(even if load transient). load is 100uA max. Slew lare within 100mV/us.

2. If information is not enough for checking the problem, please teach it to me.

3. Besides, we would like to know calculating method Vin/Vout capacitance value.

Could you teach the calculating method, please?

Best regards,