Good day!

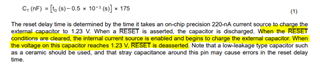

The exact part I have is TPS3808G30DBVR.

I am confused about the conditions under which the C_T-capacitor is discharged.

In the datasheet for TPS3808 it says that "When a \overline{RESET} is asserted, the capacitor is discharged." (page 11) and that "A logic low (0.3 VDD) on

\overline{MR} causes \overline{RESET} to assert."

Therefore, I would expect that the capacitor is discharged on falling edges of \overline{MR}.

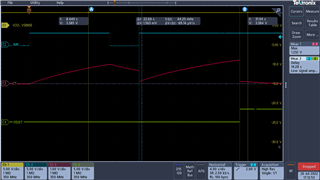

However, this is not the case for the devices I have at hand: They discharge the capacitor on rising edges of \overline{MR} and on rising edges of \overline{RESET}. (See image below)

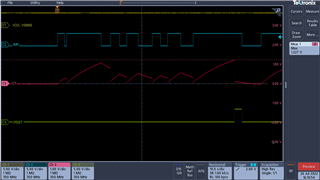

For completeness, I include here the circuit diagram:

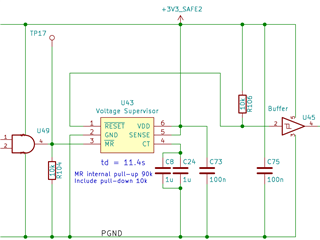

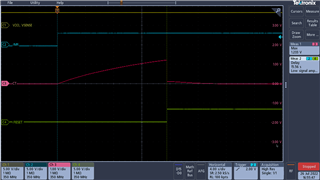

Due to this behavior the reset delay time depends on the history of the MR-pin:

When MR has been long for a long time and then goes high: 15.56s (see measurement on the right side of the screenshot below)

When MR was high, then low (for approx. 4s) and then goes high again: 14.28s. (screenshot below) Why is C_T here only discharged on the rising edge of \overline{MR} and not (as is written in the datasheet) already on the falling edge?

Thanks for your help!

Manuel