Hi

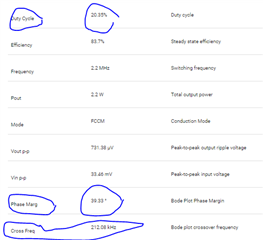

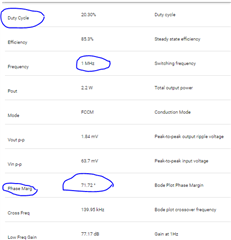

I have a query related to low phase margin (39 degree) with one of the Power rail that I have simulated and designed as well.

Generally it is recommended to go with more than 45 degree for stable system. In such case where the phase margin is less what can we do?

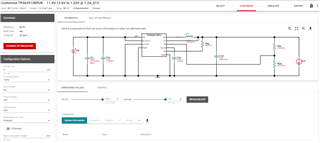

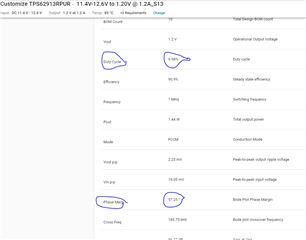

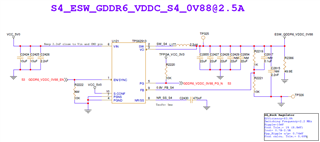

Sharing the design requirements and schematic, webbench simulation design and simulation results for your reference.

The design requirement is

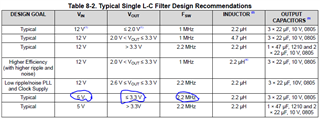

1. Vin= 5V (4.75V-5.25V)

2. Ripple=10mV

3. Vout Tole.= 1% (8.8mV)

4. Iout= 2A to 2.5A

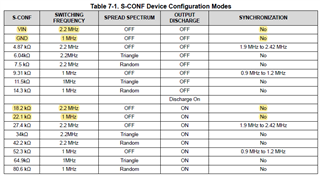

Now if I am changing the frequency from 2.2MHz to 1Mhz the phase margin is increasing.

But in the datasheet it is mentioned that for Vout less that 3.3V and Vin=5V the Fsw= 2.2MHz.

Now if I am connecting the S-CONF pin to ground to select 1MHz is it fine?

Would you please check and suggest to improve the phase margin while maintaining the duty cycle?