Other Parts Discussed in Thread: TPS23754,

Hi

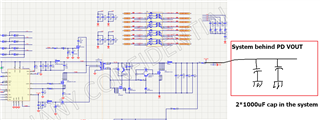

It's old bug. I had ever raised the issue on TI forums. Please help to review the website:

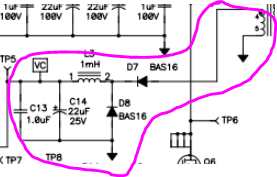

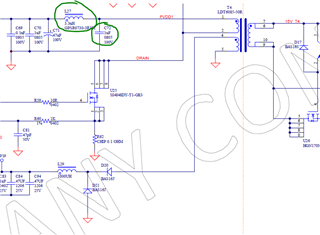

The defect rate of new PCB is higher than previous version >> VOUT is no output (15V).

We found that changing C89 from 22uF to 1uF could improve.

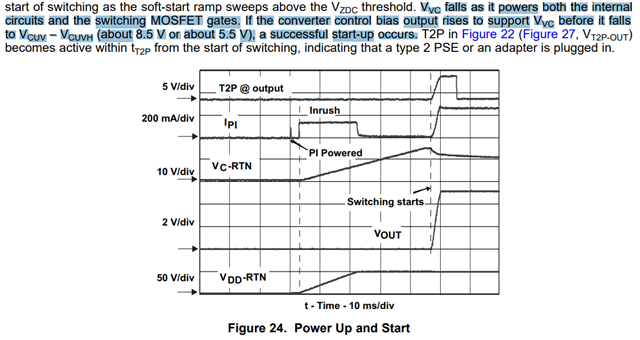

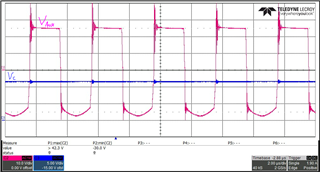

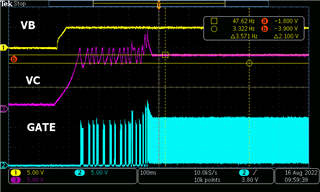

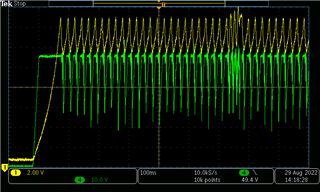

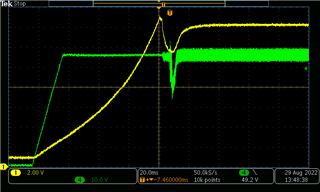

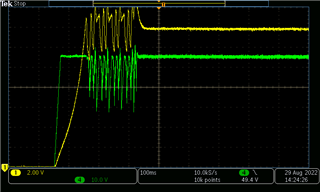

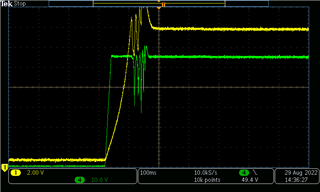

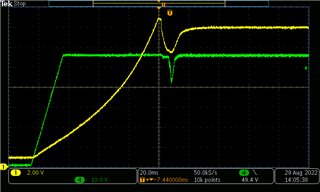

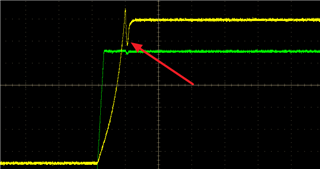

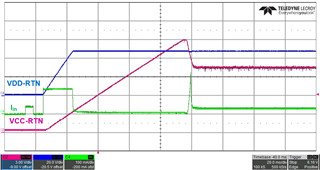

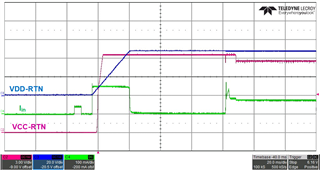

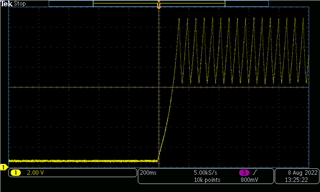

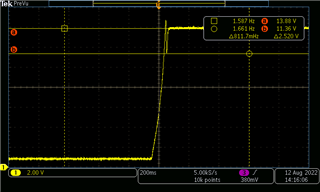

Below is VCC waveform.

C89=22uF

C89=1uF

Could you help to explain why reduce the soft-start capacitance can improve VCC waveform?

Thanks

Wendy