Other Parts Discussed in Thread: LM25143-Q1, LM5143, LM25143

Hi Team,

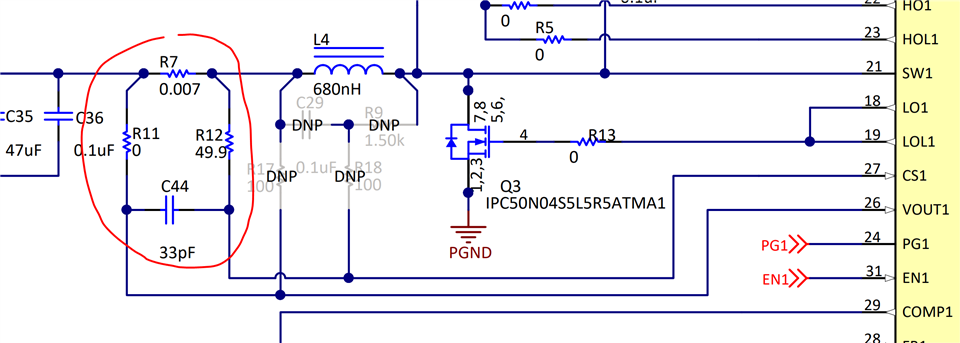

Can you help to double check the schematic of U4002 (LM5143-Q1) ?

The quick calculation toll result and FET spec are in the Zip file already.

mpci_ti_parts_20220811_pwr_Kai review.pdf

Thanks!

Kai