Hello Team,

Connections: VS=24V, Vdd=5V from external independent power supply; load at OUT1 is about 10mA

When disconnecting the 24V the VS pin should be 0V, correct? But is stays at 4.2V and the UVLO does not trigger.

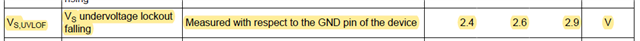

Page 8 shows UVLOF for VS for Vdd between 3.0V and 3.6V; What are these values for Vdd=5V?

This behavior is independent of the logic state of the EN pin.

According data sheet Vdd can be 5V. How can be ensured that VS = 0V when Vdd = 5V is applied?

How can you ensure that the UVLOF is detected?

Thanks and Best Regards, Hans