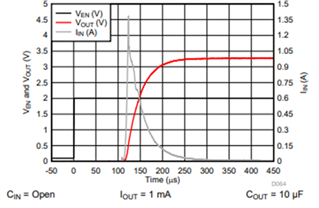

Modern electronic systems are widely used across different applications. Capacitors have become a key component and are used throughout a design for various reasons. However, when any given system is initially powered, the capacitors are uncharged and behave similar to a short-circuit. In order to charge these capacitors, the system will experience some peak current. This peak current is known as Inrush Current. The amount of inrush current experienced set by the amount of capacitance and the speed at which the voltage rises. This can be calculated using the following equation:

IINRUSH=CLOAD dV/dt

Low Dropout Voltage Regulators (LDOs) are widely used across electrical systems. These LDOs almost always require an output capacitor. As in any other system that uses capacitors, some inrush current could be experienced when the capacitor is charged during startup. This instantaneous spike of current might be enough to create system level concerns depending on the application requirements.

Therefore, inrush current can raise some questions like: Can inrush current permanently damage my device? Can inrush current exceed the specified current? Why doesn’t current limit kick in instantly? Will the device enter thermal shutdown if inrush current exceeds current limit? How to manage inrush current and prevent droop on the input voltage?

From an LDO perspective, inrush current might not be a problem. Yet, other components and/or even the traces on a PCB design could suffer from an excessive current spike.