Part Number: UCC2897

Hi

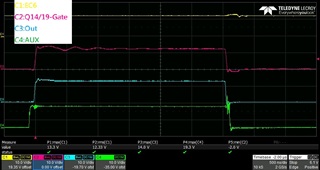

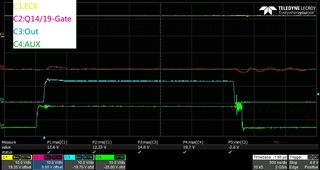

Customers can adjust RDEL from 4.99KΩ to 5.6KΩ and 10KΩ according to the Spec,

and the measurement waveform is as attached It is found that when the Q14/Q19 is adjusted to 10K,

there is no signal to turn it on. How can I adjust it?