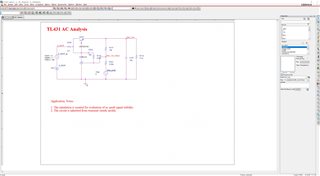

Other Parts Discussed in Thread: TL431

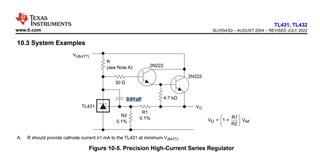

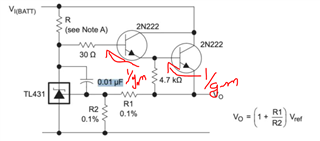

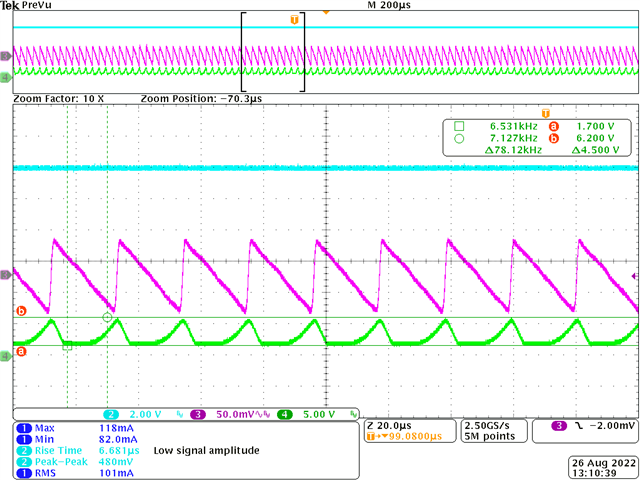

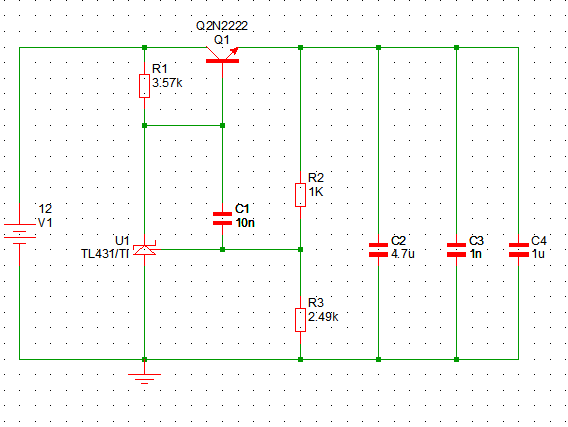

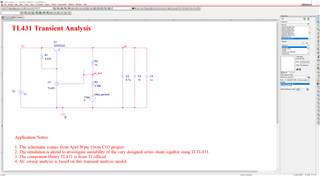

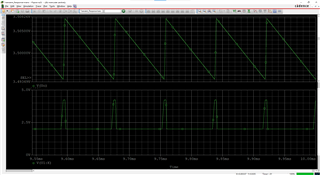

I am using TL431 to build a regulator with max. average load current of 0.5Adc and transient start-up peak current of 2Apk. This regulator is used for power of SiC mosfet driver.

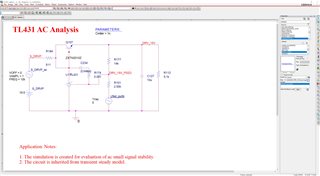

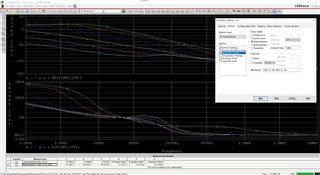

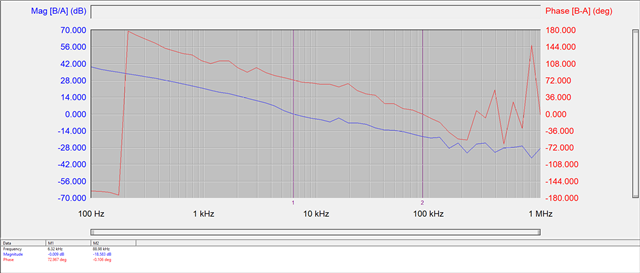

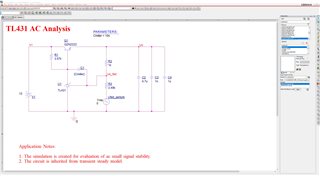

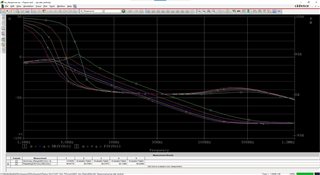

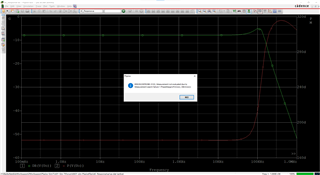

I notice there's a 0.01uF aluminum capacitor recommended in application notes. Normally compensation is necessary when using TL431, but how to evaluate this capacitor?