Other Parts Discussed in Thread: OMAPL138

We are having an issue overcoming the watchdog timer of the power supervisor during powering on our system. Are there any recommended ways of doing this correctly?

We have an OMAPL138 as our processor that can't in run BOOT mode. It is being reset every 600ms.

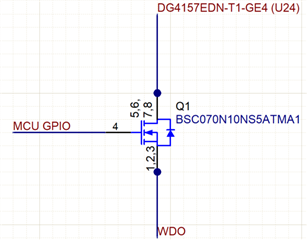

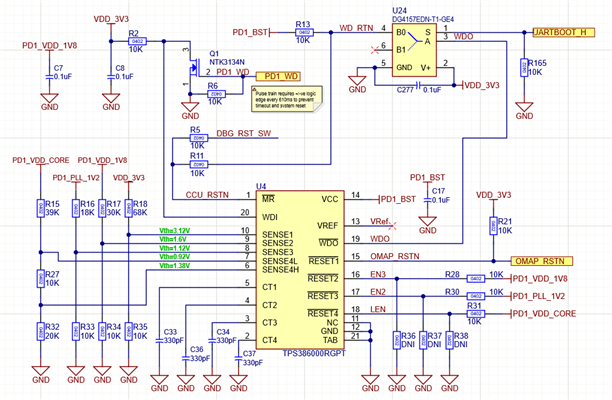

Current Schematic is below:

PD1_WD : A 600ms Pulse Train connected to a OMAP GPIO

UARTBOOT_H : High when in program BOOT mode, Low when in run BOOT mode.

DBG_RST_SW : Active Low Physical RESET switch

CCU_RSTN : Connected to Enable line of V_Core Regulator, V_Core of OMAP

OMAP_RSTN : Connected to *RESET , master reset of OMAP

Please let me know if more details are needed. Thank You.