Hi!

The following observations have been made with a pre-production-sample of the LM5123 (XLM5123). If this is a known issue and it is fixed with the production version, please let me know.

While measuring our design, we found an unusual behavior of the gate of the low side transistor, connected to "LO" on the IC.

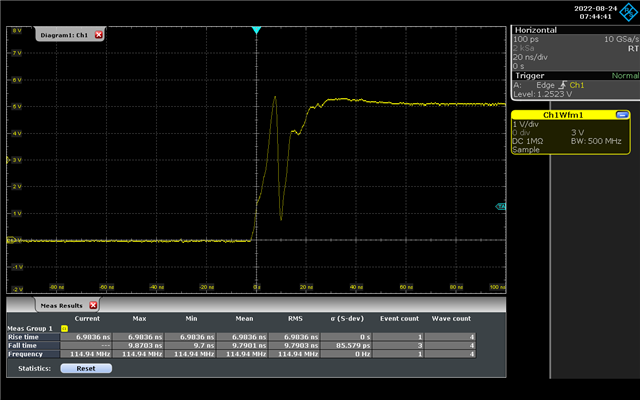

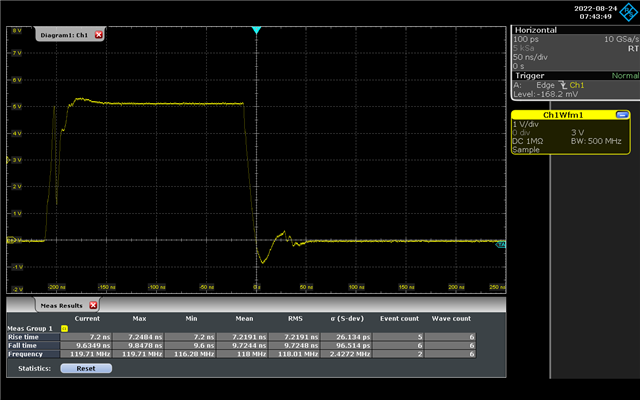

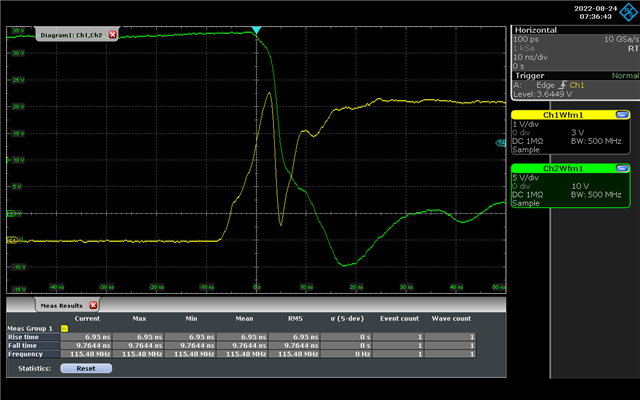

The gate driver voltage seems to break down while initially supplying the gate. The following oscilloscope measurements were made between gate and source (GND) of the low side FET, with a very short ground lead on the probe.

Close-up of rising edge:

Complete cycle of the lowside FET:

The next image shows the switch node in green for reference (values there might not be exact because the ground reference is on the other probe)

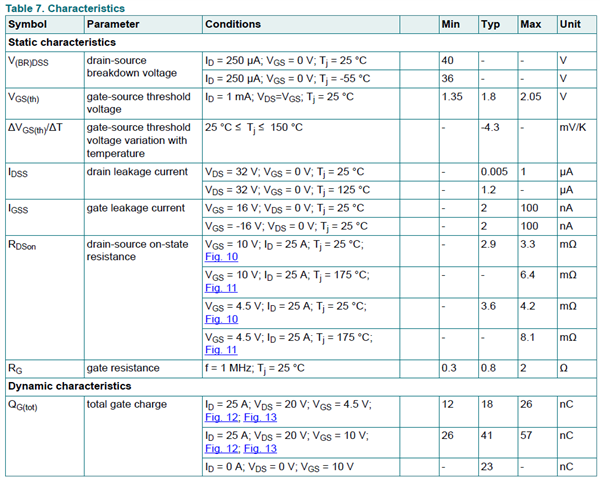

We are using the Nexperia PSMN3R2-40YLD, which has the following characteristics:

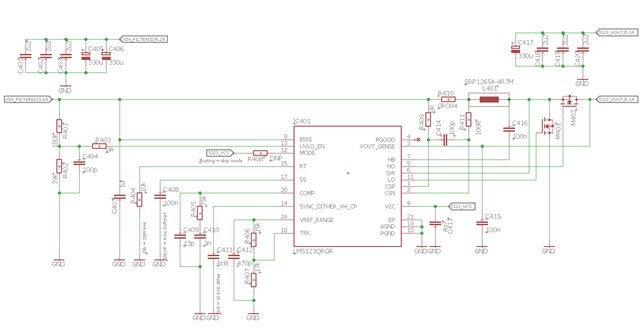

This is our schematic

The lowside FET gets relatively warm, we assume this is because the gate takes a long time to fully charge, and therefore the FET is in linear mode for longer than needed.

Can you provide us any information on this behavior? Is there anythin we can do to improve performance?

Best regards

Felix