Other Parts Discussed in Thread: LM74502-Q1, LM74502, LM74502H-Q1, LM74502H,

Hello Team,

We are trying to evaluate the LM74502-Q1 as a over voltage protection. Testing the OV cutoff behavior on the Q1 EVM we see the following behavior. It doesn't look to be intended behavior and debugging so far doesn't give any clue on the root cause.

- OV threshold is set to 36V

- Going from normal operation above 36V behavior is as expected and output turns off

- Decreasing Vin then slightly below 36V gives the behavior we see on the scope shot

- Decreasing Vin further to below 28V the behavior is again as expected and output is on

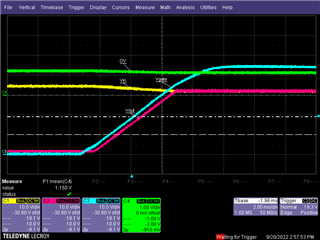

So far tests have been made without inrush current control and behavior was fine at first. Now with this behavior observed only adding the RC for inrush current control fixed the "issue".

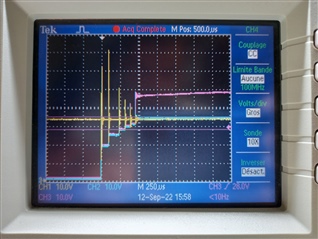

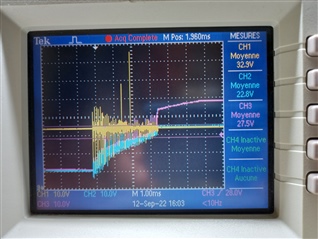

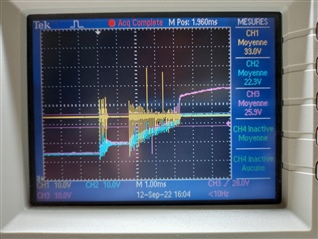

Attached some scope plots.

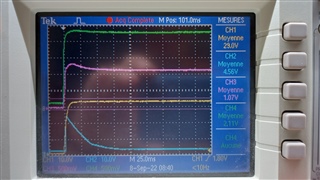

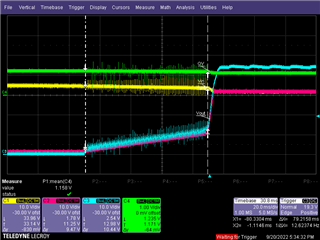

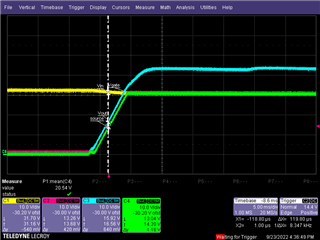

20220906_172210.jpg with Yellow = VIn, Blue = VOut, Purple = VGate

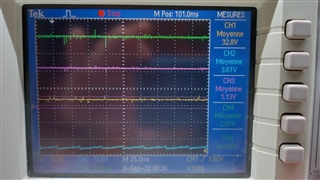

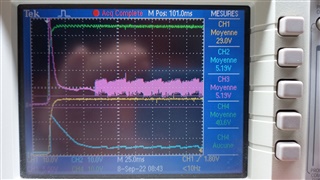

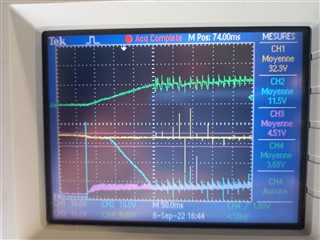

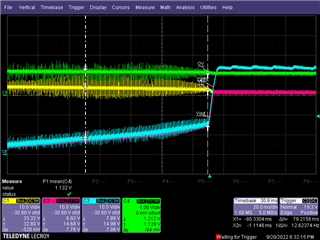

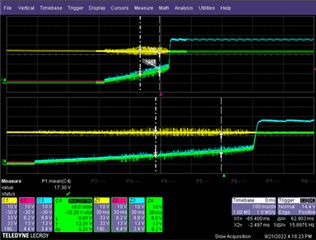

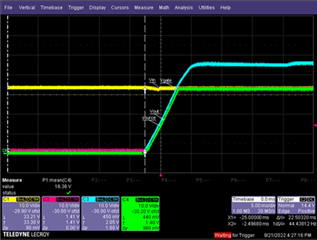

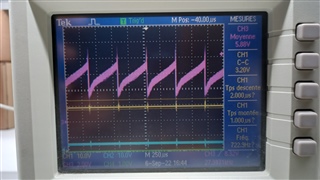

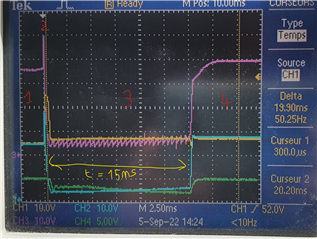

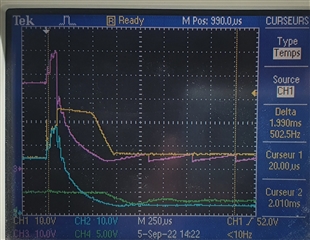

MicrosoftTeams-image (8).png, MicrosoftTeams-image (9).png, is the same test as image (8) but with a focus on the state 1 to 3.

Yellow = VIn, Blue = VOut, Purple = VGate, Green = 5V power supply on the board

1 = initial state

2= pulse 2b activation of the OV protection

3= undefined state with a Vout around 4V and Vgate at a strange voltage

4= product come back to initial state, may be because Vin go just under the threshold, but recovery time is very long.

Could you help us to understand the phenomenon to:

- Be sure we identify the good Root cause

- Suggested corrective action is the good one

- Suggested corrective action is well define

Regards,

Viktor