Other Parts Discussed in Thread: BQ25713,

Hi,

I have a problem in charging with BQ25713/BQ25713B when The pin CHRG_OK doenn't HIGH although VBUS is aroung 4.9V. In datasheet, When any fault occurs, CHRG_OK is asserted

LOW. what is possible fault in this case?

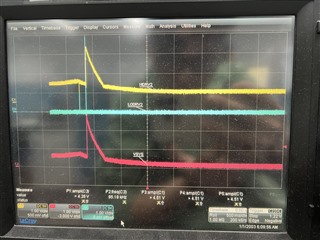

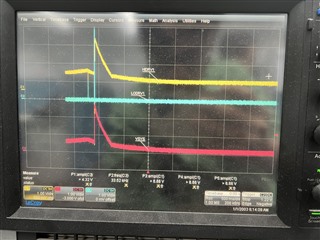

I also observed that in the initial VBUS was at 4.9V, the CHRG_OK was HIGH until the nCHARGER_ILIM_HIZ pin was HIGH, CHRG_OK was LOW as an attachment.

Best Regards,

Dien Vu