AS we discussed in our previous Case CS1046835, we've seen many problems during the power-on phase of this device.

Following TI suggestions for Case CS1046835, we've modified the circuit providing the enable introducing a delay, but our problems were only partially solved.

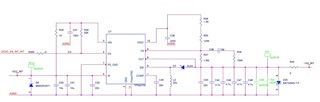

In our application (see attached circ.jpg image) we have a simple 5V to -15V inverter.

In our opinion, the problem is related to the startup current required by our load (we can roughly model our load with a simple RC circuit, where R=12ohm and C=88uF).

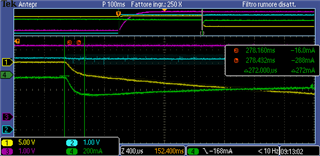

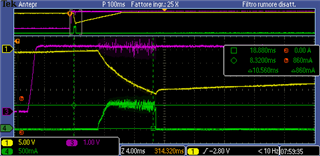

We've measured the current from the SW pin (green trace) with (load.png image) and without(no_load.png) the RC load.

In the same vaweform we show the -15V output (yellow trace) and the 5V input voltage (purple).

Looking to the 'load.png' waveform, after 2ms (maybe a soft-start time) the current reach a maximum limit and then after 8-9ms the dcdc stops switching.

My main questions are the following:

1) at point 7.4.1 the datasheet is not clear, since there are no data about the soft-start. Which is the duration? How the limitation works?

2) The datasheet never talks about an overcurrent limitation on the output side (in table 6.5 we've only found a reference to an Ilim value). Does the TPS63700 support this king of protection? If yes, how does it works?

3) is it possible to extend the soft-start time working on the feed-back circuitry? (i.e. adding a capacitor to the feedback)

Do you have any other suggestion to solve this problem?

In attachment you can find the pictures mentioned in the text above.

NO LOAD power on sequence

LOAD power on sequence

Thanks and best regards,

Fabrizio Lucini