Other Parts Discussed in Thread: TPS54J061

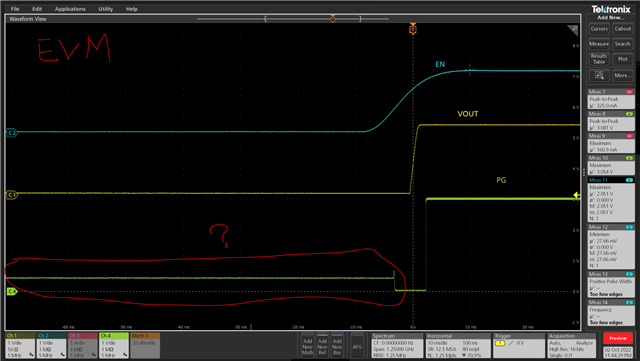

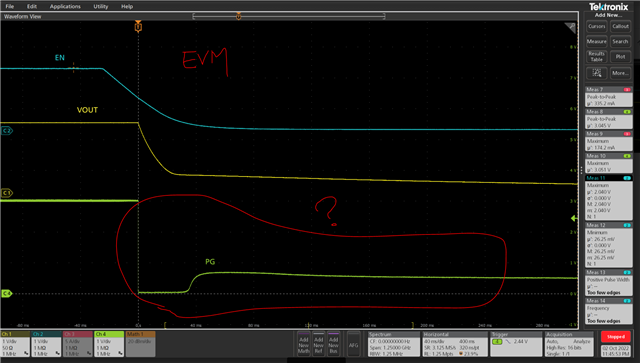

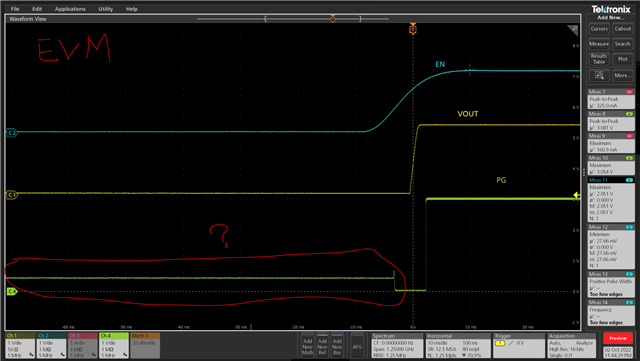

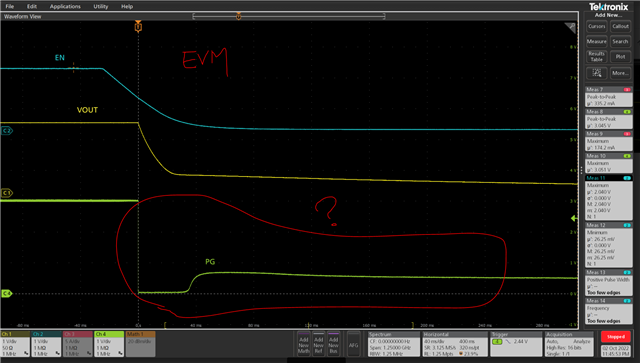

I see there is offset on Power good signal in both on/off process.

it should be 0 volt when there is no enable signal.

Or does TI has more specific spec for this unknow offset voltage of Power Good?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

I see there is offset on Power good signal in both on/off process.

it should be 0 volt when there is no enable signal.

Or does TI has more specific spec for this unknow offset voltage of Power Good?

Hello,

The power-good output is an open-drain output. I am not sure what is the status of the VIN in your case, but If the input supply fails to power up the device, the power-good signal clamps low by itself when PGOOD is pulled up through an external resistor.

Thanks

Tahar

Hi Leo,

Depending on how strong the pull-up resistor on the PGOOD pin is, it may have an offset of up to 400 mV.

![]()

I have just measured the voltage on PGOOD pin on our EVM with a 3.3KOhms pull-up resistor.

Since the sink current is 3V/3.3 KOhms = 0.9 mA, the offset was only 30 mV!

If you are getting higher than 400 mV of offset, this can be either because the PGOOD pin sinks more than 5.5 mA (which is not recommended), or some measurement set-up or grounding issue.

Regards,

Yitzhak Bolurian

Hi Yitzhak,

Could you answer the following questions:

1.

What's the PowerGood Pull low ability when enable is not active?

I think in step.2, the Power Good have ability to pull low.

The questions should be when the PowerGood start pull low? base on what condition?

(Our pull high res is 10k. It should under spec)

2.

Is POWERGOOD only pull low when enable is High? or what's PGOOD Drive's mechanism

3.

Does the TI recommend PowerGood pull high use internal VCC, not external 3V3?

Thanks

Hi Leo,

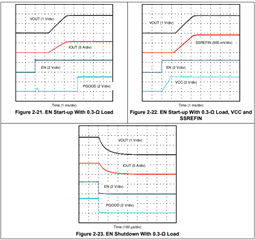

Here is a cut and paste from the TPS54J061 datasheet:

The internal LDO is not active when EN is not high. That will disable many sections of the chip including the capability of the power good pulling low.

The pull up can be connected to external voltage or the internally generated VCC. But even the VCC is off when EN is not active.

Regards,

Yitzhak

Hi, Yitzhak

Thanks for your reply.

I think TPS54J061 will not suitable to use external voltage for power good pull-high.

Because if the external pull high voltage start faster than the EN, the power good will be an unknow state.

That's may be the main reason for the offset voltage of the power good.

However, if use VCC for power good pull-high, VCC will be zero when EN is not active.

So the power good will have little offset even the power good pull low ability is not build.

What's you opinion?

Hi Leo,

Either that (Use VCC for pulling the power good up), or just do not rely on power good before EN is enabled.

If EN is controlled by the same Sequencer/Microcontroller that monitors the power-good, then the sequencer can know that the converter is off and does not need to read the state of power good to know the converter is off.

Regards,

Yitzhak