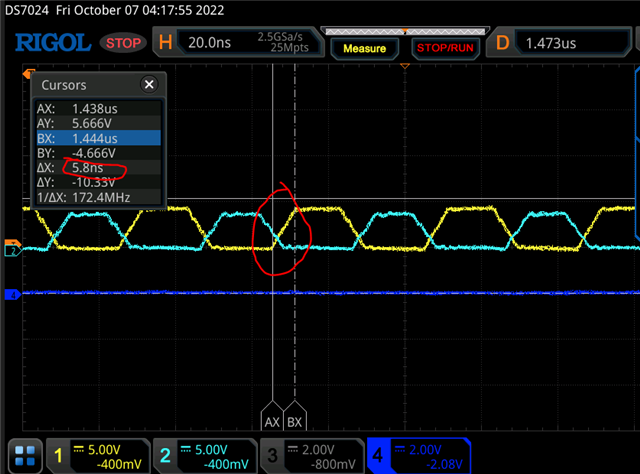

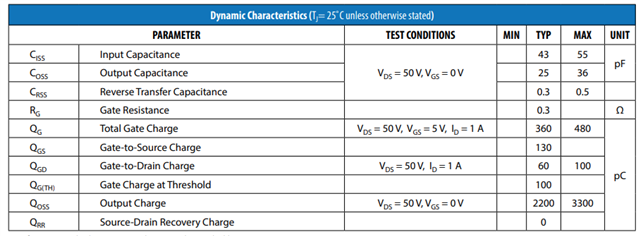

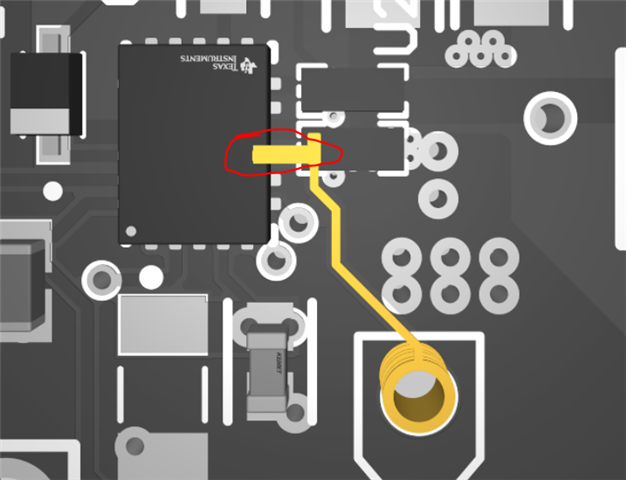

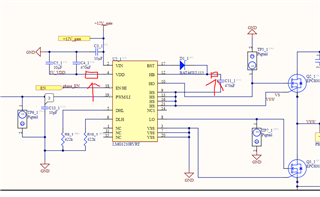

In our design, it is Hbridge GaN EPC8010(Ciss=43pF), gate driver LMG1210. The trace from gatedriver to EPC8010 is super short as shown in attached photo, there is no gate resistor in between. There is trace to a hole/via for probing(same footprint as in LMG1210EVM). So the rising/fall time should be within a ns, while we measure 6ns, as shown in the scope trace. Can you help me diagnose what is going on?