Hi Experts,

Good day.

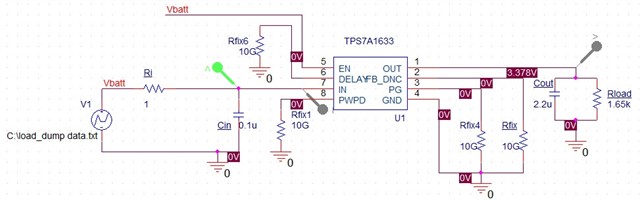

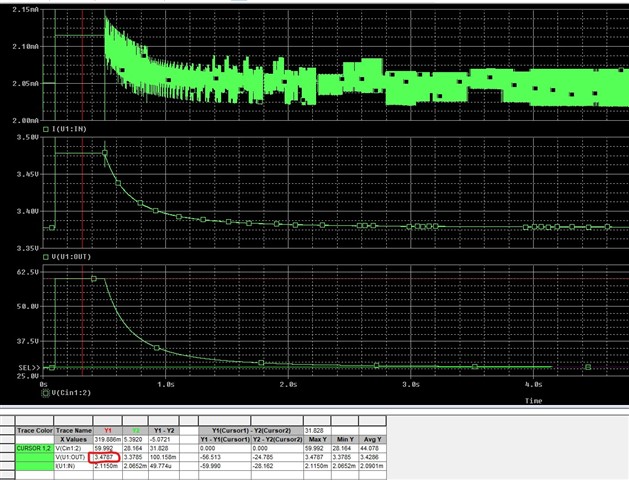

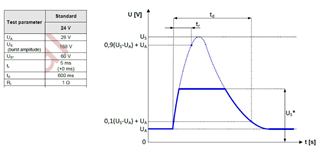

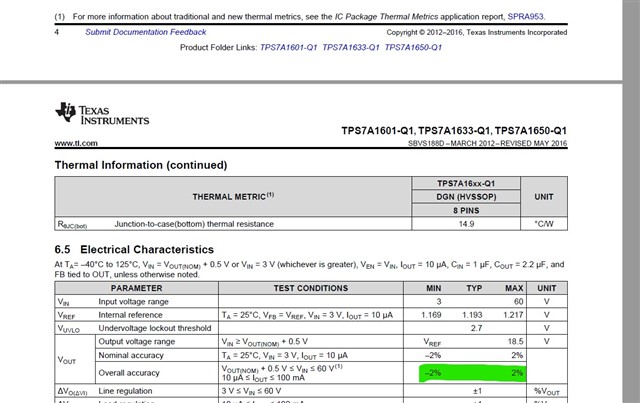

We knew that readings outside specified from absolute rating from D/S of TPS7A16A-Q1 would damage it. But we would like to know if there are some restrictions to comply in terms of rise and delay times in case of a load dump pulse transient is applied to the Vin input pin for the device TPS7A16A-Q1:

For your confirmation.

Thank you.

Regards,

Archie A.

\

\