Other Parts Discussed in Thread: , TPS62913

Hello,

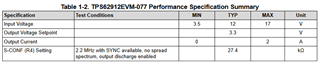

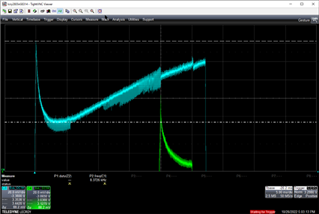

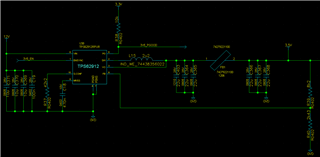

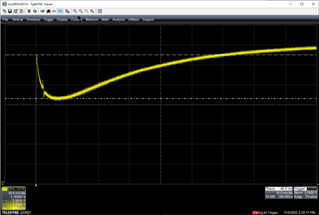

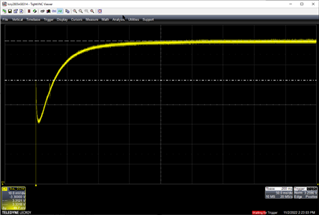

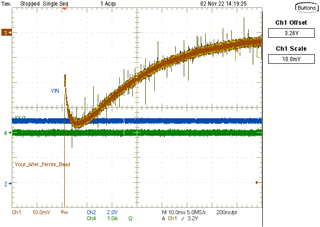

I'm using a TPS62912 in my design, and notice that there is a large undervoltage transient at the end of the soft-start sequence on all four instances of this power supply on my board. This transient is also on the evaluation board fresh out of the box with default components and jumper positions. I'm seeing the transient with both 2.2µH and 4.7µH inductors and with switching speeds of 2.2 MHz and 1 MHz.

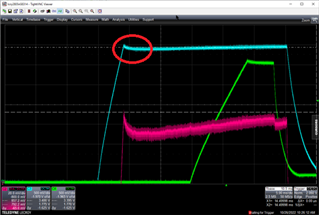

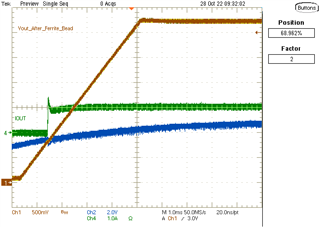

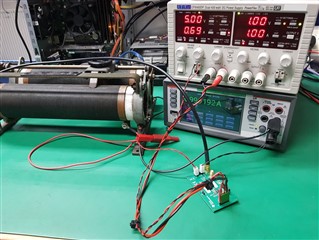

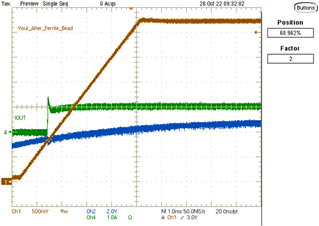

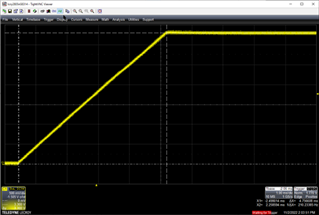

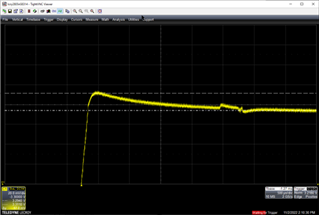

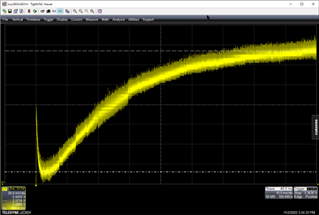

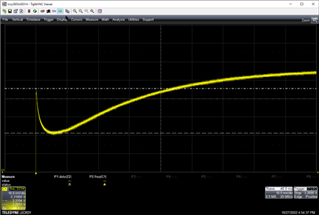

Here is a screenshot of the evaluation board output with no load fitted:

The evaluation board is generating 3.3 Volts from a 5 Volt input.

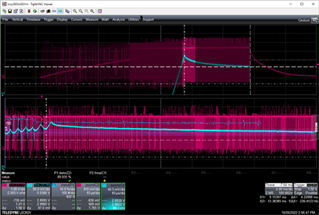

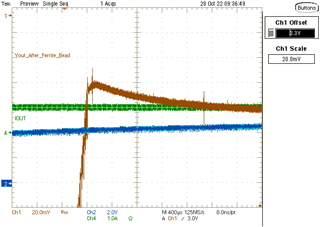

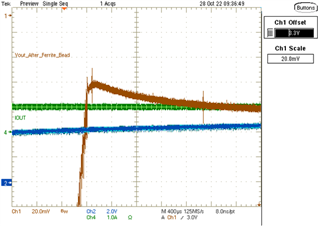

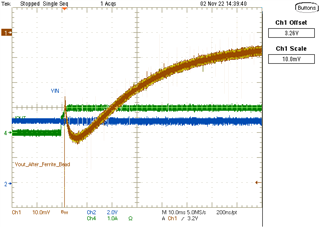

I fitted a 3.3 Ohm resistor to give a 1 Amp load, and the transient (indicated between the white cursors) increased very slightly from 24mV to 26 mV.

I tried input voltages from 12 Volts to 4.5 Volts in steps of 2 volts, and the input voltage made no difference to this transient.

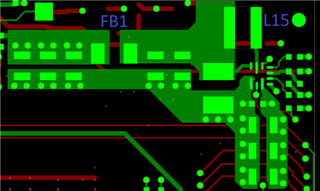

Please could I get some support on the cause of this transient and any advice on how to eliminate, or at least minimise it? I believe that working on the evaluation board would be a good starting point as the schematics and layout are publically available. I would also like to solve this issue on my board, but would prefer that the details of my design might be discussed in private.

Many thanks in advance!