Other Parts Discussed in Thread: TPSM82866A

Hi team

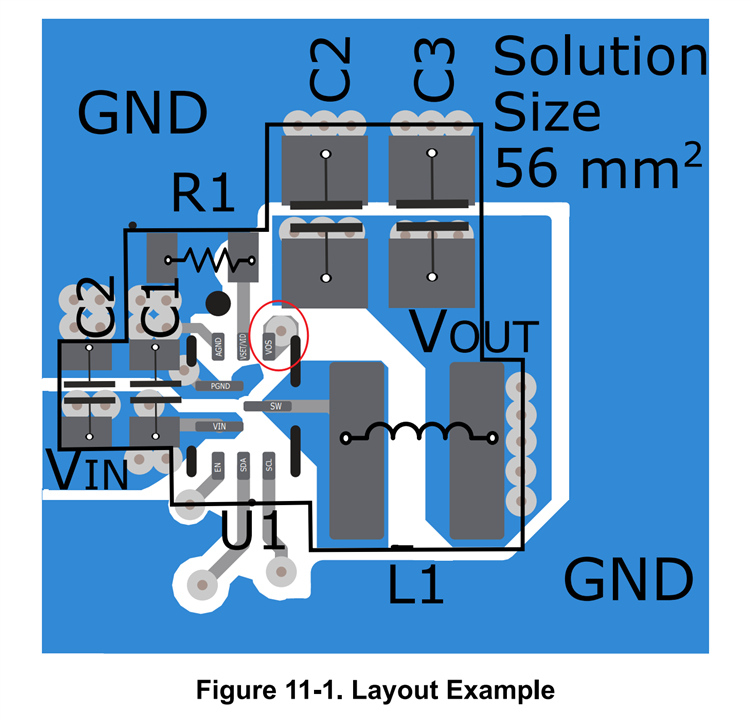

I have a questions about TPS62869 VOS pin layout:

D/S give the following layout example and here VOS pin is connected to Vout through a via, and I am wondering why VOS pin is not connected to VOUT on the top layer?

My customer suspected VOS pin may affected by SW noise and wants to know the reason of VOS pin connection shown in the D/S. I guess this connection in the example would decrease the SW noise as possible, and if the customer connects VOS and COUT on the top layer of course this would bring large SW nose because the trace is so close to SW pin.

May I know your comments?