Hello,

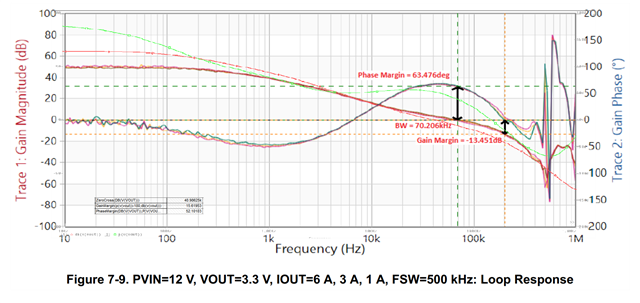

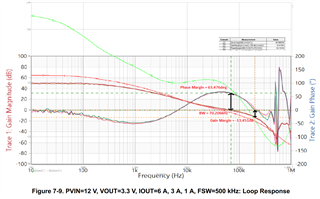

I found the loop response given in TPS7H4010EVM User's guide a bit puzzling (SNVU744 Figure 7-9 p24) :

Considering how the phase margin is taken there is no doubt on the phase offset, so i expected the phase would be around 180° when gain slope is 0 and 90° phase when gain slope is -1 which is not the case.

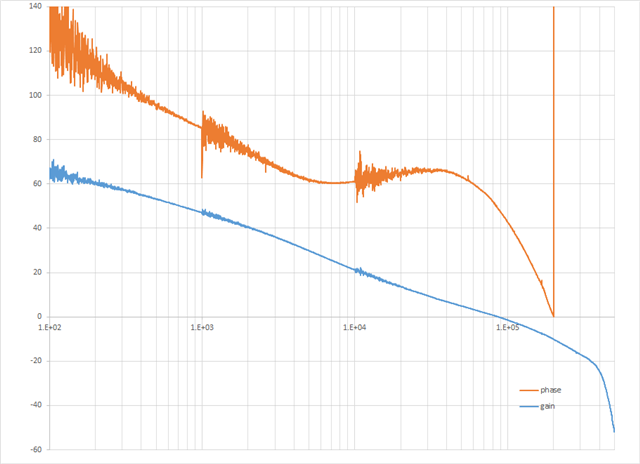

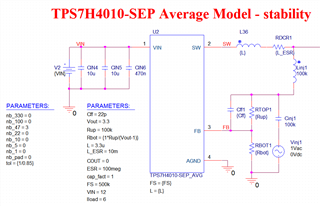

It looks like the average model of TPS7H4010-SEP is pretty much more inline with what i expect but it is not of much help if it does not match the actual converter :

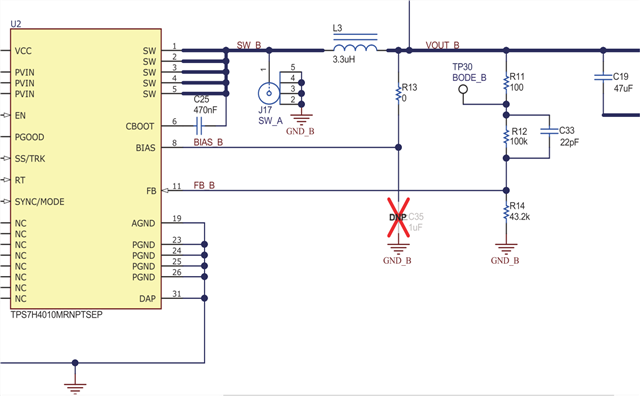

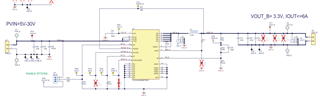

Of course i tried to match my simulation parameters (3x47uF caps are put on Vout) :

With what is actually on the eval board :

Where is the mistake ?

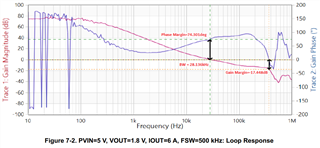

it should be also noted that the 1.8V side of the eval board have a loop response given in user's guide far closer to what i expect ( Figure 7-2 p20 ) :

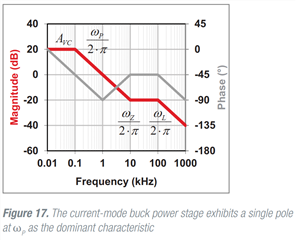

Still there is a -2 gain slope in range 1k-10kHz which to me does not match a standard current mode buck converter as for example described in slup340 Figure 17 p10 :

Thanks,