Hi, I have a few questions about the default example in the design spreadsheet

Q#1

In the design calculator, the overvoltage thresholds are VOUT_OVPnom = 5.3V and VOUT_OVPmin = 5.023V (calc cell C191).

VOUT_CV = 5V, VOUTripple = 50 mVp-p (cell C163). This means that that the maximum Vout is 5.025V (not accounting for other tolerances like the voltage regulation error).

So, the worst case Vout by design is already crossing the VOUT_OVPmin. Should we design the minimum OVP threshold higher than the maximum Vout during normal operation?

Q#2

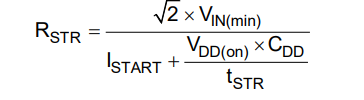

Is there an internal voltage clamp at the VDD pin to limit the voltage during start up charge from VBULK to VDD via RTRICK?

-Kelvin