Hi Team,

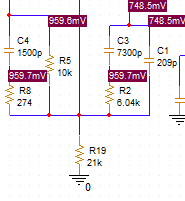

I was designing power rail for FPGA.I have used excel sheet for designing and then I tried to simulate it on PSPICE.I am not able to mate the target Ripple value and Undershoot.Please have a look and let me know what i am missing.

Designed Rail details are-

Vout -0.88V

Iout- 10A

Ripple - 12mv (peak to peak)

Undershoot - 10mV

I have attached excel sheet and PSPICE SIMULATION File.TPS544B25_Calculator Tool_0.88_10A_MGTAVCC.xlsx0.88_10A.zip