Other Parts Discussed in Thread: TPS548D21

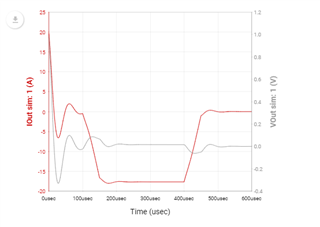

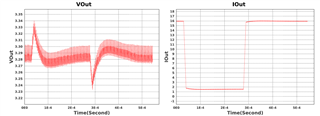

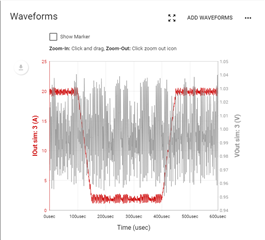

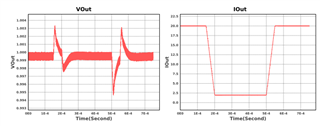

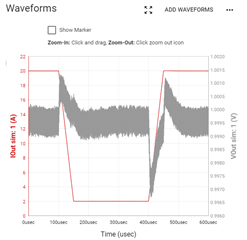

I tried to perform Load transient of any combination. Unable to get the proper waveform. Output voltage goes negative. Looks like webench model is not working. Other IC like TPS548D21, load transient works perfectly. So kindly verify load transient for TPS543C20A on your website. Also load transient pspice model is not available. Only startup and steady state model available. Kindly send load transient model.