Other Parts Discussed in Thread: , TPS7A83A, TIDA-01232

Hi all, I need some advice.

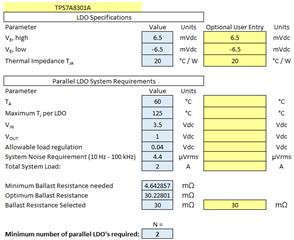

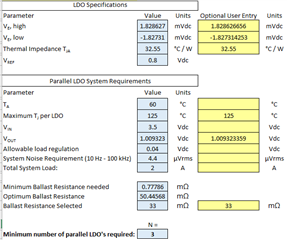

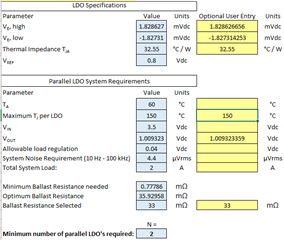

I have to use the TPS7A85 component to meet the following parameters:

Input Voltage: 3.5V

Output Voltage: 1V

Output Current: 2A

Allowable Ripple : 1mV

Voltage Tolerance: 3%

Operating Temperature: up to 60 Deg.C

EN and Power Good Pin used

I can't use a DC-DC to step down the voltage before the LDOs.

To maximize the reliability of the circuit that will have to operate continuously for a long time (years), I was thinking of using two TPS7A85.

A serial design would be very easy to implement, but could be more prone to failures.

A parallel design instead would be intrinsically safer (it would work even with a broken component), but it is more complicated to implement.

What solution do you recommend?

Thanks in advance.

Regards.