Hi Ti expert,

please have your point of view to check our schematic or suggestion.

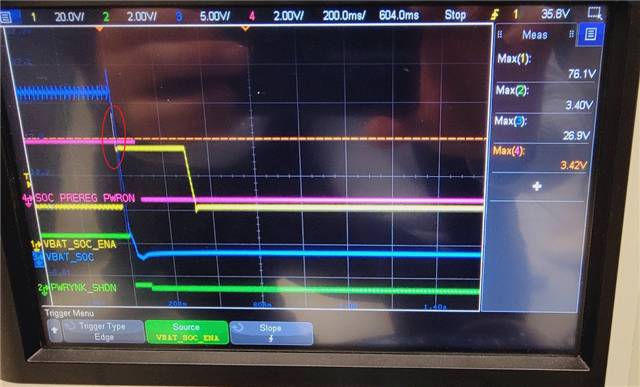

Why input spike voltage up to 76V once load dump 58V/300ms test? (40V/350ms no issue found)

CH1 YELLOW :KL30

CH2 BLUE VBAT_SOC

CH3 PWRYANK_SHDN

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Ti expert,

please have your point of view to check our schematic or suggestion.

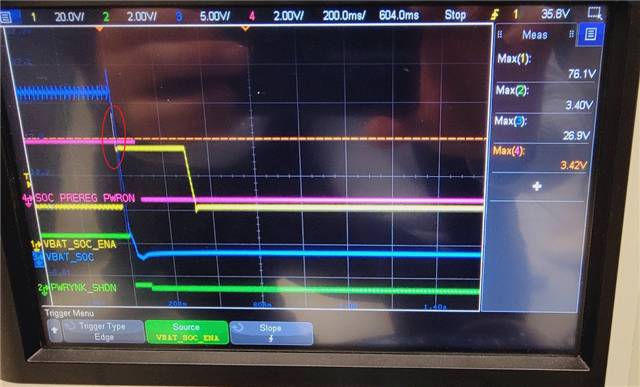

Why input spike voltage up to 76V once load dump 58V/300ms test? (40V/350ms no issue found)

CH1 YELLOW :KL30

CH2 BLUE VBAT_SOC

CH3 PWRYANK_SHDN

Hi Praveen,

Due to board already was abnormal once pulse into the input power , it's hard to capture a zoomed in waveform to share you

Hi William,

When the load dump pulse crosses 37V which is the set OV threshold , the HGATE is pulled low to turn OFF PQ1003 and PQ1004. This will block the forward current suddenly and hence will cause huge di/dt. If there is inductance in the input path, there will be voltage generated across the inductance which is equal to L x di/dt.

This voltage will add upon the input voltage and will be seen at the input of your system. Depending on the voltage and path impedance the TVS will clamp this voltage to a lower level.

In this case, customer has used SMBJ54A which has a clamping voltage of 87V at 6.9A. So, it is possible that a current of around 5A has flown through the TVS for it to clamp the voltage at 76V.

To reduce this clamping voltage, you will have to either