Team,

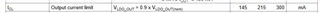

The TPS7A78 is used for a load that takes 80mA on average, but also 280mA for peaks of about 500µs.

Since the TPS7A78 limits the output current, a 4700µF electrolytic capacitor was placed at the LDO_out. On LDO_in a capacitor of 100uF was placed. More than 100µF brought no advantage.

The circuit works fine in tests.

However, the data sheet says that the capacitor at LDO_in = 10 x LDO_out and the values in the "recommended operating conditions" should be max. 1000µF and 100µF respectively.

What speaks against the solution that was tested?

What is the background behind the LDO_IN recommended operating condition above?

Are there some potential risks with this approach that would for example reduce the TPS7A78 life time?

The project is close to production and the preference would be not to do any change in the HW.

The start-up time is of course long, but this is not a problem in this application as long as we wait for Power Good

Thanks in advance,

A.