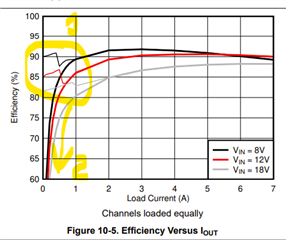

I am looking into using the LM5143 in dual output mode. I plan on having the clock's synced and use frequency dithering. I am concerned about low power efficiency. I would like better understand the efficiency graph, I understand the pulse skipping can be implemented to increase the efficiency.

So in the graph below it looks like path 1 is where the chip starts to implement the pulse skipping and low power efficiency tactics. In what conditions would the chip follow path 2 and I lose all the conditions where low power efficiency is lost.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.