Hello,

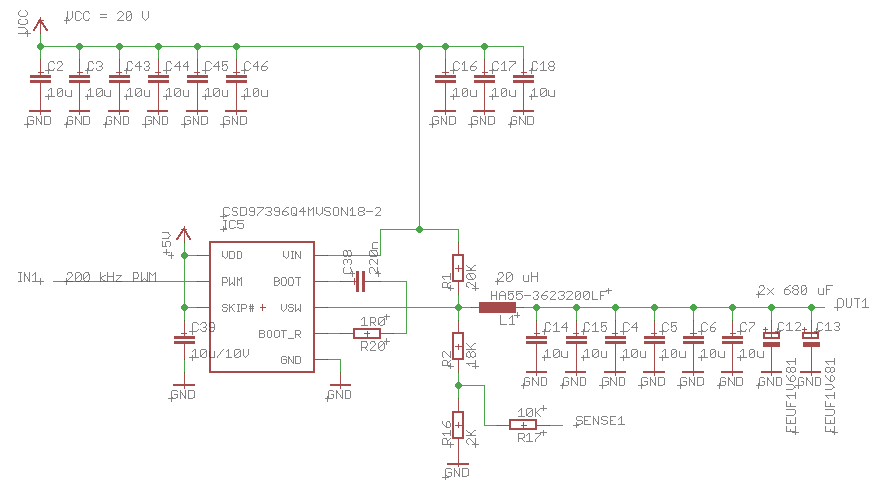

I'm working on a cooler design that uses two buck converter stages comprising the CSD97396Q4M.

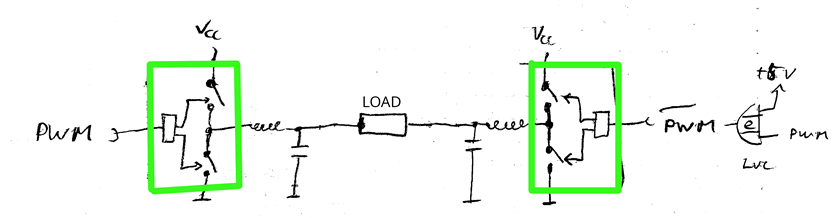

The load (peltier element) is connected to the output of the converter stages to essentially build a H-bridge.

Below find the schematic of one half of the H-bridge.

The H-bridge is controlled by a PWM signal with a frequency of 200 kHz. The other half of the H-bridge is identical but sees the inverse PWM signal.

At 50% duty cycle, both outputs of the two H-bridges have about VIN/2, so the load sees no voltage difference. Changing the duty cycle from 50% will put a voltage across the load. That's the theory.

However, this design does not work reliably. Switching the cooler unit off and on will damage the part permanently. That is, one of the FETs of the power stage fails with a short circuit (to VIN or to GND or both).

Why is this?

I'm observing strong ringing on the switching node. To reduce ringing, I increased the boot resistor to 4,7 Ohm but that did not help. Adding a Schottky diode between switching node and VIN (i.e., parallel to body diode) did not help, either.

This is the signal on one of the two switching nodes.

Although the switching node rings that does not seem to kill the part. It seems to withstand this stress.

However, powering off and on of the cooler a couple of times does kill it the part.

Please advise.

Thanks.

Dan