Hi,

I found the post below.

I was wondering if you could answer some questions about via.

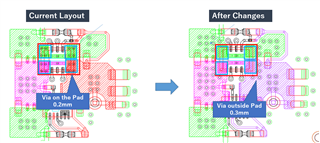

1.Would it be OK to place the via next to the pad as shown in the figure below?

2.If the via is placed next to the pad, the FB loop would be longer, but would it be OK?

3.Would it be OK to place the via on the pad and change the via diameter from 0.2 mm to 0.15 mm or 0.1 mm?

Best Regards,

Nishie

Fig.5-5

Fig.5-5