Hello,

I am trying to test a control card with UCC28180, but before testing it with the High Power plant/ baseboard, I want to test the controller card individually to check if it gives desired gate output.

For 65kHz operation,

Input of 5V is given to Vsense (pin6)

Providing 15V to Vcc(pin7)

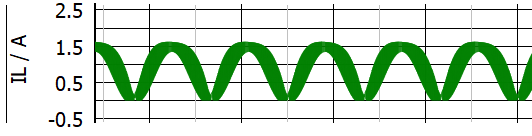

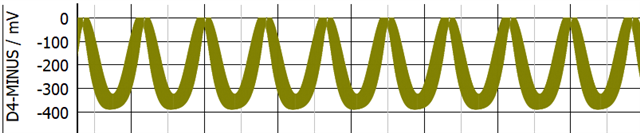

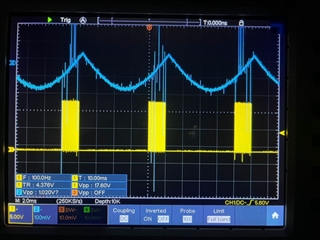

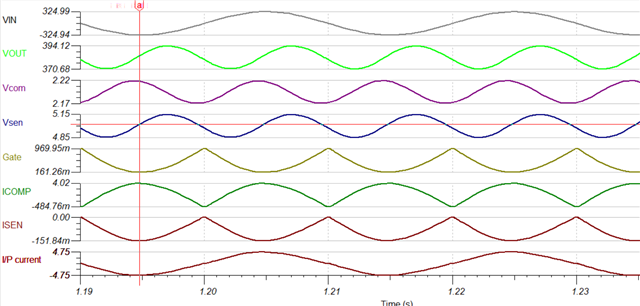

For Isense(pin3) : Through Function generator, I am planning to input a waveform that will be similar to a current sense waveform from a plant / baseboard.

But I cannot find any snapshots of the actual resulting current sense signal(going into pin3) in any of the PFC EVM board documentation to be used as a reference.

Can you please provide the same.

Regards,

.